## Novel Surface Passivation Scheme by Using p-Type AITiO to Mitigate Dynamic ON Resistance Behavior in AIGaN/GaN HEMTs—Part II

Sayak Dutta Gupta<sup>®</sup>, *Graduate Student Member, IEEE*, Vipin Joshi<sup>®</sup>, Rajarshi Roy Chaudhuri<sup>®</sup>, *Graduate Student Member, IEEE*, and Mayank Shrivastava<sup>®</sup>, *Senior Member, IEEE*

Abstract—The underlying mechanism responsible for the unique dynamic on-resistance behavior is unified by demonstrating the presence of critical drain stress voltage, above which dynamic on-resistance increases significantly, in different gate stacks. Metal-insulator-semiconductor (MIS)- and Schottky-gated HEMTs show similar dependence of critical voltage on various parameters, which establishes that gate-stack design has negligible impact on the observed phenomena. Furthermore, using the physical insights developed, this work proposes a novel surface passivation scheme to improve the dynamic performance of the device. The proposed surface passivation scheme uses p-type  $AI_{0.5}Ti_{0.5}O$  (AITiO), which is deposited over SiN<sub>x</sub> passivation (or GaN cap), and is shown to be an effective tool in improving the dynamic ON-resistance of the device by modulating the electric field in the GaN buffer. The proposed passivation scheme has avoided the critical voltage to appear for the entire drain stress voltage, stress time, and substrate bias range. Detailed computational analysis in conjunction with electroluminescence (EL) and photoluminescence (PL) studies revealed an electric field redistribution due to the p-type nature of AITiO deposited over the surface passivation/capping layer, which is responsible for relaxed electric field profile in GaN buffer and observed improvement in dynamic performance. Besides, the new observations have further helped to understand the interplay between surface conditions and GaN buffer, defining its collective role in governing the dynamic performance of GaN HEMTs. Finally, various findings and the proposal in this work have been validated for buffers having higher carbon doping and devices with p-type AITiO deposited over GaN cap instead of *in situ*  $SiN_x$  cap.

# Index Terms—AIGaN/GaN HEMTs, AITiO, carbon-doped buffer, device design, dynamic on-resistance, surface passivation.

Manuscript received August 1, 2020; revised December 20, 2020 and February 16, 2021; accepted March 4, 2021. Date of publication March 19, 2021; date of current version October 22, 2021. This work was supported by the Department of Science and Technology, Government of India, through the Technology Systems Development Programme's (TSDP) at Indian Institute of Science, Bengaluru, under Project DST/TSG/AMT/2015/294. The review of this article was arranged by Editor S. Rajan. (*Corresponding author: Sayak Dutta Gupta.*)

The authors are with the Department of Electronic Systems Engineering, Indian Institute of Science, Bengaluru 560012, India (e-mail: sayakgupta@iisc.ac.in; mayank@iisc.ac.in).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2021.3064531.

Digital Object Identifier 10.1109/TED.2021.3064531

I. INTRODUCTION

NTENTIONAL doping of GaN buffer by carbon to reduce leakage and improve breakdown [1], [2] has also emerged as a major source of dynamic ON-resistance  $(R_{ON})$  in the AlGaN/GaN HEMTs [3]-[5]. Surface passivation, on the other hand, has evolved as a key approach to improve the dynamic  $R_{\rm ON}$  of the devices [6]–[19]. Different approaches, e.g., plasma-enhanced chemical vapor deposition (PECVD)  $SiN_x$  [7], AlN [8]–[10], AlN/SiN<sub>x</sub> stack [11], GaN cap [14], NH<sub>3</sub> plasma surface treatment [15], and low pressure chemical vapor deposition (LPCVD)  $SiN_x$  [12], [13] have been reported as effective surface passivation techniques to improve the dynamic  $R_{\rm ON}$  performance of AlGaN/GaN HEMTs. Although the proposed surface passivation schemes have addressed the dynamic  $R_{\rm ON}$  phenomena, previous works did not validate its applicability for extreme scenarios like longer stress times, lower temperatures, higher current injection, and higher electric field caused by various design parameters, which can lead to the presence of a critical drain stress voltage and a significant increase in dynamic  $R_{ON}$ , as reported in part I of this work [20]. Moreover, the physical phenomena involved in dynamic performance improvement with surface passivation are not completely understood. Although conventional understanding suggests passivation of surface traps to be responsible for this improvement, recent studies [16], [17] suggest a more complex physical phenomena involved, wherein surface passivation affects buffer trap dynamics. Detailed physical insights explaining the interplay between surface and buffer trap dynamics, which collectively governs the dynamic ON-resistance behavior of HEMTs is, therefore, missing in previous works.

In this work, we analyze the impact of gate-stack and surface passivation on the dynamic performance of the device under different stress conditions. Based on the improved understanding of the physical process involved in determining the dynamic performance of the device, a novel surface passivation scheme is proposed and demonstrated. The proposed surface passivation scheme improved the dynamic  $R_{\text{ON}}$  performance of the HEMTs, independent of the GaN buffer stack. This work is arranged as follows: details of HEMT fabrication and the dynamic  $R_{\text{ON}}$  measurement routine followed for this

0018-9383 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

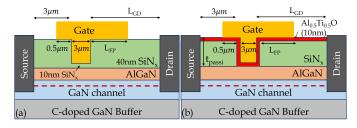

Fig. 1. Schematic of the fabricated (a)  $SiN_x$ -gated and (b)  $AI_{0.5}Ti_{0.5}O$ -gated AlGaN/GaN MISHEMTs showing the device parameters: gate–drain distance ( $L_{GD}$ ), field plate length ( $L_{FP}$ ), passivation thickness ( $t_{passi}$ ); which vary for this work. The AlTiO-gated HEMTs have a 10-nm AlTiO deposited over SiN<sub>x</sub> as passivation unlike the SiN<sub>x</sub>-gated HEMTs with only SiN<sub>x</sub> as passivation.

work is discussed in Section II. In Section III, the impact of gate-stack and surface passivation on the dynamic  $R_{ON}$ performance of GaN HEMTs as a function of various design parameters, gate-drain distance ( $L_{GD}$ ), field plate length ( $L_{FP}$ ), and passivation thickness ( $t_{passi}$ ) is discussed. In order to understand the role of gate-stack, the dynamic performance of the metal-insulator-semiconductor (MIS)-HEMTs is compared with Schottky-gated HEMTs. A novel Al<sub>0.5</sub>Ti<sub>0.5</sub>O/SiN<sub>x</sub>based passivation scheme is proposed to improve the dynamic  $R_{ON}$ . The physical mechanism behind the improved dynamic  $R_{ON}$  is then explained in Section IV. In Section V, the effectiveness of Al<sub>0.5</sub>Ti<sub>0.5</sub>O/SiN<sub>x</sub> as passivation for HEMTs with different C-doped GaN buffer is discussed, post which the work is concluded in Section VI.

#### II. DEVICE FABRICATION AND EXPERIMENTATION

A well-optimized process, as reported in our earlier work [21], was used to realize AlGaN/GaN HEMTs on a 6" (commercial grade) C-doped GaN on Si epi-stack (Stack 1). The process starts with a Ti-based ohmic contact formation followed by mesa isolation using Cl<sub>2</sub> based dry etching. In order to study the impact of gate-stack on the dynamic  $R_{\rm ON}$  of the GaN HEMTs, MISHEMTs have been processed. Ni/Au gate was deposited on 10 nm SiNx dielectric to demonstrate  $SiN_r$ -gated MISHEMTs, as shown in Fig. 1(a). The gate electrode was extended above a thicker  $SiN_r$  (SiN) passivation to form field plate (FP) structures. Besides  $SiN_x$ gate, 10 nm Al<sub>0.5</sub>Ti<sub>0.5</sub>O (AlTiO)-gated HEMTs, as shown in Fig. 1(b), were also fabricated by depositing the gate oxide using thermal atomic layer deposition (ALD), discussed in detail in our previous work [21]. In order to study the role of surface passivation on the HEMT dynamic performance, the MISHEMTs were passivated with 10 nm Al<sub>0.5</sub>Ti<sub>0.5</sub>O (AlTiO) deposited on top of SiN in the access regions before evaporation of the FP metal, as shown in Fig. 1(b). The HEMT design parameters, viz.  $L_{GD}$ ,  $L_{FP}$ , and  $t_{passi}$ , were also varied across the test chip to study their role on dynamic  $R_{\rm ON}$  of the device. It is worth highlighting here that the HEMTs were processed using a well-optimized process [21] under similar process conditions and surface cleaning to minimize any process-related variability across the devices.

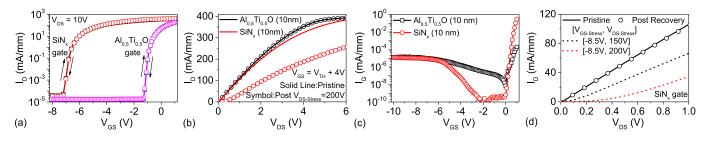

Fig. 2(a) depicts the transfer characteristics  $(I_D-V_{GS})$  of the fabricated MISHEMTs. While SiN-gated HEMTs showed

typical depletion mode operation with a deep-seated threshold voltage ( $V_{\text{TH}}$ ) of -7 V, Al<sub>0.5</sub>Ti<sub>0.5</sub>O-based HEMTs showed a significant positive shift in  $V_{\text{TH}}$  ( $\approx -1$  V) due to the p-type nature of the gate oxide [21]. The p-type oxide, however, achieved this positive  $V_{\text{TH}}$  shift while retaining the other HEMT performance metrices at par with the best reports till date [21]. This can be seen from Fig. 2(a), which shows excellent ON and OFF-state performance of the fabricated HEMTs with negligible  $I_D - V_{GS}$  hysteresis, irrespective of the gate oxide. The output characteristics  $(I_D - V_{DS})$  of the fabricated MISHEMTs, as seen from Fig. 2(b), also shows both the HEMTs to have a similar ON-current ( $\approx 400 \text{ mA/mm}$ ) and pristine  $R_{ON}$ . The gate leakage  $(I_G - V_{GS})$  of both AlTiOand SiN-gated HEMTs, as depicted in Fig. 2(c), shows very low leakage in inversion region. However, in the accumulation region, there is a significant increase in leakage for the SiN-gated HEMTs. This is attributed to the low conduction band offset between AlGaN and SiN [22]-[24]. Moreover, in order to study the effectiveness of the proposed AlTiO-based surface passivation scheme, Schottky and Al<sub>0.5</sub>Ti<sub>0.5</sub>O-gated HEMTs were also processed over HEMT stack having GaN buffer with higher C-doping than Stack 1 (Stack 2).

Dynamic  $R_{\rm ON}$  ( $\Delta R_{\rm ON}$ ) for the MISHEMTs was evaluated by stressing the device [17] for 100  $\mu$ s in OFF-state immediately followed by an  $I_D-V_{\rm DS}$  sweep at  $V_{\rm GS} = 1$  V. In some cases, the devices were also subjected to longer stress times to probe the stress time dependence of  $\Delta R_{\rm ON}$ . The OFF-state stress was realized by biasing the HEMT using 26XX SMUs at  $V_{\rm GS-Stress} = V_{\rm TH}-2$  V and OFF-state drain stress voltage ( $V_{\rm DS-Stress}$ ) varied from 0 to 200 V. Here,  $\Delta R_{\rm ON}$  was evaluated as follows:

$$\Delta R_{\rm oN} \text{ (in \%)} = \frac{R_{\rm Post-Stress} - R_{\rm Pristine}}{R_{\rm Pristine}} \times 100 \tag{1}$$

where  $R_{\text{Pristine}}$  and  $R_{\text{Post-Stress}}$  is the HEMT's  $R_{\text{ON}}$  in pristine and post stress conditions, respectively. The  $R_{\text{ON}}$  is measured from inverse slope of  $I_D-V_{\text{DS}}$  for  $V_{\text{DS}} = 0.25$  to 0.5 V. Fig. 2(d) shows a typical  $I_D-V_{\text{DS}}$  characteristics of the MISHEMTs obtained during the measurement routine. It shows a significant  $V_{\text{DS-Stress}}$  dependent increase in  $R_{\text{ON}}$ , which results in an observable  $\Delta R_{\text{ON}}$  in the SiN-gated HEMTs. No such degradation was however, observed in the AITiO-gated HEMTs, as seen from Fig. 2(b). Besides, the measurement routine also included a 180 s recovery time to recover the MISHEMTs to pristine condition after measuring  $R_{\text{Post-Stress}}$  and before the next stress cycle, as depicted in Fig. 2(d).

#### III. IMPACT OF GATE-STACK AND NOVEL SURFACE PASSIVATION

#### A. Gate-Stack Design

The dynamic performance of Schottky-gated GaN HEMTs with C-doped buffer, dealt in Part I of this work [20], revealed a critical  $V_{\text{DS-Stress}}$  ( $V_{cr}$ ) beyond which the  $\Delta R_{\text{ON}}$  of the HEMTs degraded significantly. It is important to understand the role of gate-stack on the dynamic performance of the HEMTs, especially because GaN MISHEMTs have recently gained much prominence due to lower gate leakage and higher

Fig. 2. (a) Dual sweep transfer ( $I_D-V_{GS}$ ) characteristics, (b) output ( $I_D-V_{DS}$ ) characteristics, and (c) gate leakage ( $I_G-V_{GS}$ ) characteristics of the fabricated Al<sub>0.5</sub>Ti<sub>0.5</sub>O- and SiN<sub>x</sub>-gated HEMTs depicting superior HEMT performance. The  $R_{ON}$  of the Al<sub>0.5</sub>Ti<sub>0.5</sub>O- and SiN<sub>x</sub>-gated HEMTs was 8.9  $\Omega$ -mm and 9.4  $\Omega$ -mm, respectively. (b) Also shows a significant increase in  $R_{ON}$  post a  $V_{DS-Stress}$  of 200 V for 100  $\mu$ s in the SiN<sub>x</sub>-gated HEMTs, while no such degradation was observed for the Al<sub>0.5</sub>Ti<sub>0.5</sub>O-gated HEMTs with similar pristine  $R_{ON}$ . (d) Typical  $I_D-V_{DS}$  characteristic of the SiN<sub>x</sub>-gated HEMTs for  $V_{GS} = 1 V$ , obtained during the dynamic  $R_{ON}$  measurement routine. Devices show significant increase in ON-resistance as a function of OFF-state stress ( $V_{DS-Stress}$ ). The devices recovered to pristine condition after 180 s recovery post the stress, as seen from the overlapping  $I_D-V_{DS}$  characteristics with the pristine HEMT.

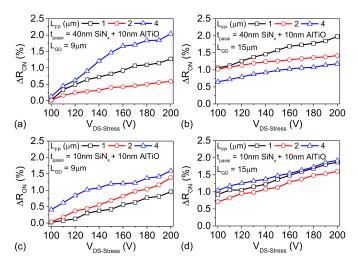

Fig. 3. Dynamic  $R_{ON}$  for SiN<sub>x</sub>-gated GaN HEMTs as a function of lateral device parameter: field plate length ( $L_{FP}$ ) for gate–drain distance ( $L_{GD}$ ) of (a) 9  $\mu$ m and (b) 15  $\mu$ m showing a device parameter dependent critical voltage ( $V_{cr}$ ) in the HEMTs. (c) Similar dependence of critical voltage on the device design parameters:  $L_{FP}$  and  $L_{GD}$  for both the Schottky and SiN<sub>x</sub>-gated GaN HEMTs on C-doped buffer. Both Schottky- and MIS-HEMTs had a 40-nm SiN<sub>x</sub> passivation ( $t_{passi} = 40$  nm). Besides,  $V_{cr}$  is defined as the  $V_{DS-Stress}$  for which  $\Delta R_{ON} > 10\%$ .

gate overdrive. In order to analyze the impact of gate-stack, SiN-gated MISHEMTs were fabricated on the same C-doped GaN buffer as the Schottky HEMTs.

Dynamic performance of the SiN-gated devices as a function of  $V_{\text{DS-Stress}}$  is shown in Fig. 3. Fig. 3(a) and (b) shows a  $V_{cr}$  beyond which the  $\Delta R_{\text{ON}}$  degrades significantly for the GaN MISHEMTs too. Fig. 3(a) also shows the  $V_{cr}$  to be dependent on  $L_{\text{FP}}$  in the SiN-gated HEMTs.  $V_{cr}$  for the HEMTs with  $L_{\text{GD}} = 9 \ \mu\text{m}$  is seen to reduce from ~170 to ~140 V as  $L_{\text{FP}}$  is increased from 1 to 4  $\mu$ m. The  $V_{cr}$  however, shows reduced dependence on  $L_{\text{FP}}$  for larger  $L_{\text{GD}}$  (15  $\mu$ m), as seen in Fig. 3(b). Besides, the MISHEMTs with larger  $L_{\text{FP}}$  also showed a higher  $\Delta R_{\text{ON}}$  for  $V_{\text{DS-Stress}} > V_{cr}$ .

Fig. 3(c) summarizes the dependence of  $V_{cr}$  on  $L_{GD}$  and  $L_{FP}$  for the SiN-gated HEMTs and compares it with the Schottky-gated HEMTs, discussed in Part I of this work [20]. Fig. 3(c) shows a similar dependence of  $V_{cr}$  on  $L_{FP}$  and  $L_{GD}$  for the HEMTs, irrespective of them being Schottkyor MIS-gated. The  $V_{cr}$  for both the Schottky- and MIS-gated HEMTs with  $L_{GD} = 9 \ \mu$ m, is seen to reduce as the  $L_{FP}$  is increased from 1 to 4  $\mu$ m. Besides, both the HEMTs show a reduced dependence of  $V_{cr}$  on  $L_{FP}$  for  $L_{GD} = 15 \ \mu$ m. It is worth highlighting here that both the HEMTs, which demonstrated this similar dependence of  $V_{cr}$  on  $L_{GD}$  and  $L_{FP}$ , had 40 nm SiN as passivation with the only difference being

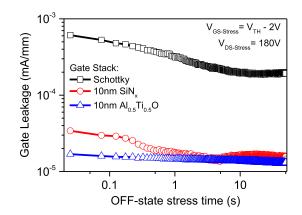

Fig. 4. Gate leakage during OFF-state stress for Schottky, 10 nm SiN<sub>x</sub> and 10 nm Al<sub>0.5</sub>Ti<sub>0.5</sub>O gated HEMTs. The gate leakage in Schottky-gated HEMTs under OFF-state is  $\sim$ 20× greater than the MISHEMTs.

in the gate-stack. Besides, similar behavior was observed in spite of a  $\sim 20 \times$  higher OFF-state gate leakage in the Schottky HEMTs as compared to the SiN HEMTs, as seen in Fig. 4. These observations confirm negligible impact of gate-stack and gate leakage on the  $V_{cr}$  as well as  $\Delta R_{ON}$  behavior of C-doped GaN HEMTs. Rather, similar dependence of  $V_{cr}$  on

Fig. 5. Dynamic  $R_{ON}$  of MISHEMTs, with 10 nm Al<sub>0.5</sub>Ti<sub>0.5</sub>O deposited on top of SiN<sub>x</sub> (AITiO/SiN passivation), as a function of field plate length ( $L_{PP}$ ) for gate–drain distance ( $L_{GD}$ ) of (a), (c) 9  $\mu$ m, and (b) and (d) 15  $\mu$ m. HEMTs have AITiO deposited on top of (a) and (b) 40 nm SiN<sub>x</sub> and (c) and (d) 10 nm SiN<sub>x</sub> passivation, respectively. The dynamic  $R_{ON}$ for these HEMTs did not show any critical voltage till 200 V. Moreover, any dependence on  $L_{PP}$ ,  $L_{GD}$  and thickness of SiN<sub>x</sub> under AITiO layer was also found to be missing.

Fig. 6. Device schematic depicting the electron trapping phenomena leading to observed  $\Delta R_{\rm ON}$  characteristics of HEMTs with SiN<sub>x</sub> passivation. (a) Represents the condition in which applied  $V_{\rm DS-Stress}$  is small enough to prevent carrier injection into the GaN buffer. This is supported by a lower ionization probability of buffer traps due to lower field across the GaN stack, which leads to negligible  $\Delta R_{\rm ON}$ . (b) Represents the condition in which applied  $V_{\rm DS-Stress}$  is high enough to cause sufficient carrier injection which combined with increased buffer trap ionization probability at higher electric fields results in significant  $\Delta R_{\rm ON}$ . The estimated electron path is represented by a dashed line with linewidth representing the magnitude of leakage current.

$L_{\text{GD}}$  and  $L_{\text{FP}}$  for the Schottky as well as MIS gated HEMTs establishes that the  $V_{cr}$  is dependent on the channel electric field.

## B. Surface Passivation

Different surface passivation schemes were also analyzed for their impact on  $\Delta R_{\rm ON}$  behavior of the device. While the devices discussed in Fig. 3 had SiN as surface passivation, a different passivation scheme with 10 nm Al<sub>0.5</sub>Ti<sub>0.5</sub>O grown as surface protection layer over SiN passivation (AlTiO/SiN passivation), as seen in Fig. 1(b), is discussed in this section. As  $V_{cr}$  and  $\Delta R_{\rm ON}$  were found to have negligible dependence

Fig. 7. Dynamic  $R_{ON}$  of the MISHEMTs as a function of (a), (c) substrate bias ( $V_{sub}$ ), and (b) and (d) stress time ( $t_{Stress}$ ). The Dynamic  $R_{ON}$  of MISHEMTs with only SiN passivation is shown in (a) and (b), while (c) and (d) show the performance of HEMTs with AITiO deposited on top of SiN passivation. The HEMTs with only SiN passivation show a critical voltage ( $V_{cr}$ ), beyond which the  $\Delta R_{ON}$  increases significantly, to be a strongly dependent on  $V_{sub}$  and  $t_{Stress}$ . The HEMTs with AITiO/SiN passivation however, showed low dynamic  $R_{ON}$  with no critical voltage till 200 V even for higher positive  $V_{sub}$  and longer  $t_{Stress}$ . Device dimension:  $L_{GD} = 9 \ \mu m$ and  $L_{FP} = 4 \ \mu m$ . SiN passivated HEMTs have 40 nm SiN, while AITiO/SiN passivated HEMTs have  $t_{passi} = 40 \ nm SiN_x + 10 \ nm Al_{0.5} Ti_{0.5}O$ .

on gate-stack, these HEMTs also used AlTiO as the gate oxide for ease of processing.

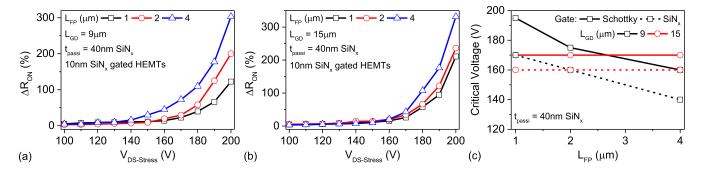

Fig. 5 shows extremely low  $\Delta R_{ON}$  in AlGaN/GaN HEMTs with AlTiO/SiN passivation. Fig. 5(a) and (b) shows no  $V_{cr}$  till 200 V in the AlTiO/SiN passivated HEMTs, even for larger  $L_{GD}$  or  $L_{FP}$ , unlike the HEMTs with only SiN passivation as seen in Fig. 3. It should also be noted that the demonstrated improvement in  $\Delta R_{ON}$  was achieved despite similar gate leakage seen in both SiN and AlTiO gated HEMTs, as seen in Fig. 4. This further validates the  $V_{cr}$  to be a gate-stack independent phenomenon.

Furthermore, HEMTs with 10 nm Al<sub>0.5</sub>Ti<sub>0.5</sub>O deposited over a thinner SiN passivation, also did not show any  $V_{cr}$  till 200 V. This improvement was independent of  $L_{GD}$  and  $L_{FP}$ , as depicted in Fig. 5(c) and (d). These observations clearly establish AlTiO/SiN as a promising surface passivation scheme for improving the  $\Delta R_{ON}$  behavior of C-doped AlGaN/GaN HEMTs. Given the fact that the observed  $\Delta R_{ON}$  and  $V_{cr}$  in these devices were due to trapping of electrons in the acceptor traps introduced by C-doping in GaN buffer (discussed in part I of this work [20]), improvement in buffer induced  $\Delta R_{ON}$  degradation by surface modification signifies a complex surface-buffer interplay in these HEMTs.

## IV. MECHANISM RESPONSIBLE FOR DYNAMIC R<sub>ON</sub> IMPROVEMENT

### A. Observations From Carrier Trapping Dynamics

The mechanism governing the presence of a  $V_{cr}$  in  $\Delta R_{ON}$  of AlGaN/GaN HEMTs was proposed and justified in Part-I

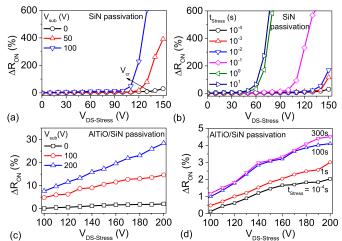

of this work [20], which is summarized in Fig. 6. As per the proposed mechanism,  $V_{cr}$  was found to be due to the presence of a critical electric field in the access region and associated buffer trap ionization as well as carrier trapping. It was found to be a strong function of stress duration, carriers injected into GaN buffer, buffer trap ionization probability, electric field strength, substrate bias, and temperature. Externally increasing the carrier injection in the GaN buffer and carrier trapping by increasing positive substrate bias voltage  $(V_{sub})$  and stress duration  $(t_{Stress})$  was found to drastically reduce  $V_{cr}$  of the device. This validated the proposed phenomena and provided a method to externally modulate the  $V_{cr}$  of the device. Such a reduction in  $V_{cr}$  with increasing positive  $V_{sub}$  and  $t_{Stress}$  was also observed in the SiN-gated HEMTs with SiN passivation, as seen in Fig. 7(a) and (b), respectively.

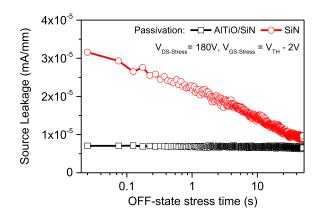

Devices with AlTiO/SiN surface passivation were also studied to investigate dependence of its dynamic performance on stress time and carrier injection into the GaN buffer. For higher  $V_{\text{sub}}$  and  $t_{\text{Stress}}$ , a much lower  $V_{cr}$  is expected. Fig. 7(c) and (d) show the impact of  $V_{\rm sub}$  and  $t_{\rm Stress}$  on  $\Delta R_{\rm ON}$  of the device. It can be observed from Fig. 7(c) that though the  $\Delta R_{\rm ON}$  increases when carrier injection into GaN buffer was increased by applying positive  $V_{sub}$ ,  $V_{cr}$  was not observed for these devices up to stress voltage of 200 V despite applying a very high  $V_{sub}$  of 200 V. Similarly, Fig. 7(d) shows the absence of  $V_{cr}$  for devices with AlTiO/SiN as surface passivation even for stress time as high as 300 s. However, devices with only  $SiN_x$  surface passivation, as seen in Fig. 7(b) and discussed in Part I of this work [20], had a significantly reduced  $V_{cr}$ when stress time was increased from 100  $\mu$ s to 10 s. Furthermore, it should be noted that a reduction in  $V_{cr}$  for higher positively applied  $V_{sub}$ , as seen in Fig. 7(a) and discussed in Part I of this work [20], indicates increased buffer trapping in these devices as  $V_{\rm sub}$  increases carrier injection in the GaN buffer. However, the same seems to be missing/relaxed in devices with proposed AlTiO/SiN surface passivation scheme. This is confirmed in Fig. 8, which shows missing carrier trapping (i.e., no change in source current with respect to time) in AlTiO/SiN passivated devices when compared to SiN passivated devices, which show significant presence of carrier trapping (i.e., drop in source current as a function of time).

## B. Impact of Surface Passivation on Electric Field

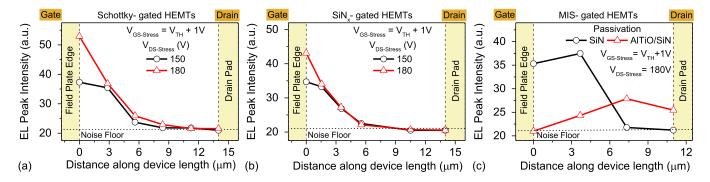

As devices with AlTiO/SiN passivation show a lower source-drain leakage current as compared to SiN passivated devices, as seen in Fig. 8, it suggests a reduction in electric field magnitude in the channel. Furthermore, the absence of  $V_{cr}$  even under application of very high  $V_{sub}$  and increased  $t_{Stress}$ , indicates reduced trap ionization probability under a given stress condition, which also suggests relaxation in trap ionization or electric field in the access region. In order to further analyze this aspect, a lateral electric field profile was analyzed using electroluminescence (EL) spectroscopy. Fig. 9(a) and (b) shows the EL line scans of the Schottky and SiN gated MISHEMTs along the gate-drain access

Fig. 8. OFF-state source current as a function of stress time for devices having SiN and AITiO/SiN passivations. The device dimensions are:  $L_{GD} = 15 \ \mu m, L_{FP} = 2 \ \mu m.$

region. Irrespective of the gate-stack, the EL line spectra of the GaN HEMTs show a similar electric field peaking near the FP edge followed by an exponential decay in the gate-drain access region. Fig. 9(c), depicting the EL line scan of AlTiO/SiN passivated HEMTs, however, shows that unlike SiN passivated MISHEMTs, the introduction of  $Al_{0.5}Ti_{0.5}O$  significantly redistributes the electric field in the gate-drain access region with no field peak near the FP edge. Field relaxation and lower OFF-state source current combined with the observations from Section IV-A establish relaxed trap ionization and carrier trapping to be responsible for improved dynamic performance of the AlTiO/SiN passivated devices.

## *C.* Why AlTiO-Based Passivation Scheme Improved Dynamic R<sub>ON</sub> Performance?

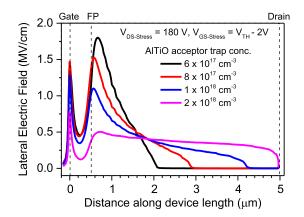

In Section II-B, modulation of lateral electric field profile was found to be responsible for the improvement in the dynamic performance of the device. As both Schottkyand SiN-gated HEMTs have similar electric field profiles [Fig. 9(a) and (b)], the HEMTs showed similar dependence of  $V_{cr}$  on the device parameters [Fig. 3(c)]. On the other hand, while EL line scans show a relaxation in the electric field near the FP edge with AlTiO/SiN surface passivation, it was difficult to experimentally evaluate its impact on the source-drain leakage current. In order to further analyze the effect, TCAD based analysis was carried out on devices with AlTiO/SiN as surface passivation layer using a well-calibrated TCAD framework [2], [25]. Since AlTiO is found to be a p-type oxide with Al% controlling its p-type property, which we confirmed using Hall measurements [21], the doping in AlTiO was modeled as shallow acceptor traps with an activation energy of  $E_V + 0.1 \text{ eV}$ . It should be noted that since the activation energy is not experimentally known, a lower value was selected so as to ensure ionization of acceptor states to contribute holes in AlTiO under thermal equilibrium, which corroborates with experimentally measured value [21]. Fig. 10 compares the electric field profile as a function of acceptor trap concentration in AlTiO. It shows a field redistribution in

Fig. 9. EL intensity line scans along gate–drain access regions of (a) Schottky-gated and (b) SiN<sub>x</sub>-gated HEMTs showing similar electric field profile for both the HEMTs, with the EL intensity peaking near the field plate edge. The device dimensions are:  $L_{GD} = 15 \ \mu m$ ,  $L_{FP} = 1 \ \mu m$  and SiN<sub>x</sub> passivation thickness of 40 nm. (c) EL line scans along gate–drain access regions of HEMTs with AlTiO/SiN passivation showing redistributed electric field with no field peak at field plate edge, unlike HEMTs with only SiN<sub>x</sub> passivation. The device parameters are:  $L_{GD} = 15 \ \mu m$  and  $L_{FP} = 4 \ \mu m$ .

Fig. 10. Lateral electric field in HEMTs with AITiO/SiN surface passivation showing redistributed electric field profile with reduced peak at gate edge and field plate edge as acceptor traps in AITiO is increased. These acceptor traps are introduced in the AITiO due to their p-type nature.

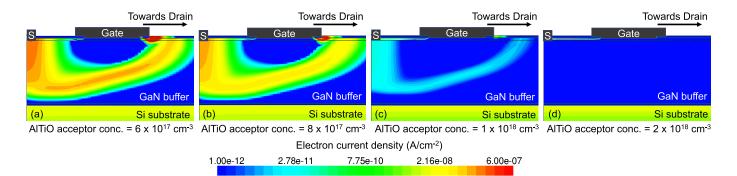

the gate–drain access region with an increase in acceptor trap concentration or Al doping. This field redistribution results in a field relaxation near the gate edge as well as an FP edge, similar to the EL line scan extracted field profile shown in Fig. 9(c). Reduction in peak field value will drastically reduce the trap ionization probability and hence, increase  $V_{cr}$ . Additionally, the resulting current contours shown in Fig. 11 depicts a reduction in carrier injection into the buffer as p-type doping concentration, represented by acceptor states density in AlTiO, is increased.

The above observations establish that reduced trap ionization probability due to efficient field redistribution and reduced carrier injection into GaN buffer results in the observed improvement in the dynamic performance of the device with AlTiO/SiN as surface passivation. Furthermore, field relaxation by the proposed surface passivation ensures the negligible impact of  $L_{GD}$  and  $L_{FP}$  on the dynamic performance of the device as seen in Fig. 5. A similar argument holds true for the absence of  $V_{cr}$  even with higher  $V_{sub}$  of 200 V and higher  $t_{Stress}$  of 300 s, as seen in Fig. 7(c) and (d), respectively. The above arguments strongly suggest AlTiO surface protection-induced field relaxation be responsible for the observed improvement in the dynamic performance of the device. It should, however, also be noted that a possibility of AlTiO surface passivation scheme shifting the detrapping time constant outside the poststress measurement window, i.e., to submicroseconds time scales, cannot be completely ruled out.

These findings further help to understand the interplay between surface and buffer conditions, which was also highlighted in our recent works [26], [27]. In part-I we noticed that as far as surface conditions do not change the electric field profile in the buffer region, dynamic ON-resistance was independent of surface conditions/leakage [20]. However, if surface conditions modulate the electric field in the GaN buffer, as observed in this work, the dynamic behavior of GaN HEMT is affected accordingly.

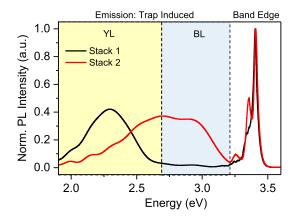

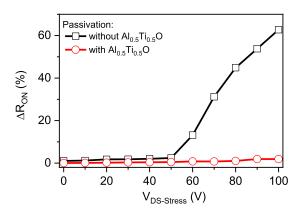

#### V. INDEPENDENCE OF C-DOPING IN GAN BUFFER

To establish the proposed technique as a promising approach for improving the dynamic performance of the device, the performance of the proposed surface passivation scheme was further examined on a different epi-stack having a higher C-doping concentration (Stack 2). High C-doping in Stack 2 has been verified using the photoluminescence (PL) spectra of the stack using a 325 nm laser, as shown in Fig. 12. The PL spectra of Stack 2 show a broad luminescence in the yellow luminescence (YL) and blue luminescence (BL) band, which is attributed to the C-doping induced acceptor traps in the GaN buffer [28], [29]. Furthermore, Fig. 12 shows the presence of a strong BL in Stack 2 unlike in Stack 1, which is due to a higher C-doping in Stack 2, as reported in [28]. Fig. 13 shows the  $\Delta R_{\rm ON}$  performance of the HEMTs on Stack 2. In the case of the device without AlTiO over GaN cap,  $V_{cr}$  was found to be as low as 50 V due to very high C-doping in the GaN buffer. On the other hand, devices with AlTiO passivation did not show  $V_{cr}$  for the measured range. This establishes surface protection of SiN passivation or GaN cap by deposition of AlTiO, as a novel passivation scheme, to mitigate  $\Delta R_{ON}$  in GaN HEMTs, irrespective of the doping in GaN buffer.

Fig. 11. Current density contours extracted for a AITiO/SiN passivated HEMT with acceptor trap concentrations of (a)  $6 \times 10^{17}$  cm<sup>-3</sup>, (b)  $8 \times 10^{17}$  cm<sup>-3</sup>, (c)  $1 \times 10^{18}$  cm<sup>-3</sup>, and (d)  $2 \times 10^{18}$  cm<sup>-3</sup> in AITiO. The contours depict a reduction in leakage current through the GaN buffer as the acceptor trap concentration in the passivation is increased. The contours were extracted at a  $V_{\text{DS-Stress}}$  of 200 V and  $V_{\text{GS-Stress}} = V_{\text{TH}} - 2V$  while keeping a shorter  $L_{\text{GD}}(=5 \ \mu\text{m})$  to account for the worst case.

Fig. 12. PL spectra of C-doped GaN buffers: Stack 1 and Stack 2 using a 325 nm laser. BL and YL peaks due to C-doping induced buffer traps shows higher C-doping in Stack 2 as compared to Stack 1.

Fig. 13. Dynamic  $R_{ON}$  of HEMTs with and without Al<sub>0.5</sub>Ti<sub>0.5</sub>O protection layer over GaN cap as surface passivation scheme. The HEMTs have a GaN buffer with high C-doping (Stack 2). Unlike the devices with conventional passivation, HEMTs with AITiO deposited over GaN cap did not show any critical voltage.

## VI. CONCLUSION

Dependence of dynamic ON-resistance in AlGaN/GaN HEMTs with C-doped buffer on gate-stack and surface passivation was studied. Gate-stack design was found to have a negligible impact on the HEMT's dynamic ON-resistance. Both  $SiN_x$  and Schottky-gated HEMTs depicted very similar dynamic behavior, i.e., both depicted the presence of a critical drain stress voltage above which signature of carrier trapping in GaN buffer was observed and HEMT's dynamic ON-resistance increased significantly. To mitigate this phenomenon, p-type Al<sub>0.5</sub>Ti<sub>0.5</sub>O was introduced on top of SiN<sub>x</sub> passivation and GaN capping layer. In the presence of an AlTiO-based novel passivation scheme, dynamic ON-resistance was found to be missing with no critical voltage observed for the entire measurement range. The effectiveness of the passivation scheme was established even under conditions that would reduce the critical voltage such as longer stress times, positive substrate bias, and higher C-doping in the buffer. This was attributed to the redistribution of the electric field across the entire access region with a relaxed electric field near the gate/field plate edge, which was earlier localized at the gate and field plate edge. These findings further help to understand the interplay between surface conditions and buffer. In part-I, we noticed that as far as surface conditions do not change the electric field profile in the buffer region, dynamic ON-resistance was independent of surface conditions/leakage. However, if surface conditions modulate the electric field in the GaN buffer, the dynamic behavior of GaN HEMT is affected accordingly, as observed in this work. Redistribution of lateral electric field and reduced electric field strength near field plate edge mitigated the possibility of electron trapping in the acceptor traps of GaN buffer, which resulted in the improved dynamic performance of C-doped AlGaN/GaN HEMTs.

#### ACKNOWLEDGMENT

Sayak Dutta Gupta and Rajarshi Roy Chaudhuri would like to thank DST INSPIRE for their fellowship. Authors would also like to acknowledge National Nanofabrication Centre (NNfC) at Indian Institute of Science, Bangalore, funded by MeitY and DST, Government of India.

#### REFERENCES

E. Bahat-Treidel, F. Brunner, O. Hilt, E. Cho, J. Wurfl, and G. Trankle, "AlGaN/GaN/GaN:C back-barrier HFETs with breakdown voltage of over 1 kV and low R<sub>ON</sub> × A," *IEEE Trans. Electron Devices*, vol. 57, no. 11, pp. 3050–3058, Nov. 2010, doi: 10.1109/TED.2010.2069566.

- [2] V. Joshi, S. P. Tiwari, and M. Shrivastava, "Part I: Physical insight into carbon-doping-induced delayed avalanche action in GaN buffer in AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 66, no. 1, pp. 561–569, Jan. 2019, doi: 10.1109/TED.2018.2878770.

- [3] O. Hilt, E. Bahat-Treidel, E. Cho, S. Singwald, and J. Wurfl, "Impact of buffer composition on the dynamic on-state resistance of high-voltage AlGaN/GaN HFETs," in *Proc. 24th Int. Symp. Power Semiconductor Devices*, Jun. 2012, pp. 345–348, doi: 10.1109/ ISPSD.2012.6229092.

- [4] G. Verzellesi *et al.*, "Influence of buffer carbon doping on pulse and AC behavior of insulated-gate field-plated power AlGaN/GaN HEMTs," *IEEE Electron Device Lett.*, vol. 35, no. 4, pp. 443–445, Apr. 2014, doi: 10.1109/LED.2014.2304680.

- [5] M. J. Uren *et al.*, "Leaky dielectric' model for the suppression of dynamic *R<sub>ON</sub>* in carbon-doped AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 64, no. 7, pp. 2826–2834, Jul. 2017, doi: 10.1109/TED.2017.2706090.

- [6] R. Vetury, N. Q. Zhang, S. Keller, and U. K. Mishra, "The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs," *IEEE Trans. Electron Devices*, vol. 48, no. 3, pp. 560–566, Mar. 2001, doi: 10.1109/16.906451.

- [7] R. Chu et al., "1200-V normally off GaN-on-Si field-effect transistors with low dynamic on-resistance," *IEEE Electron Device Lett.*, vol. 32, no. 5, pp. 632–634, May 2011, doi: 10.1109/LED.2011. 2118190.

- [8] A. D. Koehler *et al.*, "Atomic layer epitaxy AlN for enhanced AlGaN/GaN HEMT passivation," *IEEE Electron Device Lett.*, vol. 34, no. 9, pp. 1115–1117, Sep. 2013, doi: 10.1109/LED.2013.2274429.

- [9] Z. Tang, S. Huang, X. Tang, B. Li, and K. J. Chen, "Influence of AlN passivation on dynamic ON-resistance and electric field distribution in high-voltage AlGaN/GaN-on-Si HEMTs," *IEEE Trans. Electron Devices*, vol. 61, no. 8, pp. 2785–2792, Aug. 2014, doi: 10.1109/TED.2014.2333063.

- [10] H. Wang, C. Liu, Q. Jiang, Z. Tang, and K. J. Chen, "Dynamic performance of AlN-passivated AlGaN/GaN MIS-high electron mobility transistors under hard switching operation," *IEEE Electron Device Lett.*, vol. 36, no. 8, pp. 760–762, Aug. 2015, doi: 10.1109/LED.2015.2450695.

- [11] Z. Tang, S. Huang, Q. Jiang, S. Liu, C. Liu, and K. J. Chen, "High-voltage (600-V) low-leakage low-current-collapse AlGaN/GaN HEMTs with AlN/SiN<sub>x</sub> passivation," *IEEE Electron Device Lett.*, vol. 34, no. 3, pp. 366–368, Mar. 2013, doi: 10.1109/LED.2012.2236638.

- [12] Y. Shi et al., "Normally OFF GaN-on-Si MIS-HEMTs fabricated with LPCVD-SiNx passivation and high-temperature gate recess," *IEEE Trans. Electron Devices*, vol. 63, no. 2, pp. 614–619, Feb. 2016, doi: 10.1109/TED.2015.2510630.

- [13] Z. Zhang *et al.*, "Studies on high-voltage GaN-on-Si MIS-HEMTs using LPCVD Si<sub>3</sub>N<sub>4</sub> as gate dielectric and passivation layer," *IEEE Trans. Electron Devices*, vol. 63, no. 2, pp. 731–738, Feb. 2016, doi: 10.1109/TED.2015.2510445.

- [14] G.-Y. Lee, P.-T. Tu, and J.-I. Chyi, "Improving the off-state characteristics and dynamic on-resistance of AlInN/AlN/GaN HEMTs with a GaN cap layer," *Appl. Phys. Exp.*, vol. 8, no. 6, Jun. 2015, Art. no. 064102, doi: 10.7567/APEX.8.064102.

- [15] A. P. Edwards, J. A. Mittereder, S. C. Binari, D. S. Katzer, D. F. Storm, and J. A. Roussos, "Improved reliability of AlGaN-GaN HEMTs using an NH<sub>3</sub> plasma treatment prior to SiN passivation," *IEEE Electron Device Lett.*, vol. 26, no. 4, pp. 225–227, Apr. 2005, doi: 10.1109/LED.2005.844694.

- [16] Y. Saito, R. Tsurumaki, N. Noda, and K. Horio, "Analysis of reduction in lag phenomena and current collapse in field-plate AlGaN/GaN HEMTs with high acceptor density in a buffer layer," *IEEE Trans. Device Mater. Rel.*, vol. 18, no. 1, pp. 46–53, Mar. 2018, doi: 10.1109/TDMR.2017.2779429.

- [17] W. M. Waller *et al.*, "Control of buffer-induced current collapse in AlGaN/GaN HEMTs using SiNx deposition," *IEEE Trans. Electron Devices*, vol. 64, no. 10, pp. 4044–4049, Oct. 2017, doi: 10.1109/TED.2017.2738669.

- [18] A. Koudymov, V. Adivarahan, J. Yang, G. Simin, and M. A. Khan, "Mechanism of current collapse removal in field-plated nitride HFETs," *IEEE Electron Device Lett.*, vol. 26, no. 10, pp. 704–706, Oct. 2005, doi: 10.1109/LED.2005.855409.

- [19] A. D. Koehler *et al.*, "Impact of surface passivation on the dynamic ON-resistance of proton-irradiated AlGaN/GaN HEMTs," *IEEE Electron Device Lett.*, vol. 37, no. 5, pp. 545–548, May 2016, doi: 10.1109/LED.2016.2537050.

- [20] S. D. Gupta, V. Joshi, R. R. Chaudhuri, and M. Shrivastava, "Part I: Physical insights into dynamic R<sub>ON</sub> behavior and a unique timedependent critical stress voltage in AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 68, no. 11, pp. 5720–5727, Nov. 2021, doi: 10.1109/TED.2021.3109847.

- [21] S. D. Gupta *et al.*, "Positive threshold voltage shift in AlGaN/GaN HEMTs and E-mode operation by Al<sub>x</sub>Ti<sub>1-x</sub>O based gate stack engineering," *IEEE Trans. Electron Devices*, vol. 66, no. 6, pp. 2544–2550, Jun. 2019, doi: 10.1109/TED.2019.2908960.

- [22] T. Hashizume, S. Ootomo, T. Inagaki, and H. Hasegawa, "Surface passivation of GaN and GaN/AlGaN heterostructures by dielectric films and its application to insulated-gate heterostructure transistors," J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct. Process., Meas., Phenomena, vol. 21, no. 4, pp. 1828–1838, 2003, doi: 10.1116/1.1585077.

- [23] A. Chini, J. Wittich, S. Heikman, S. Keller, S. P. DenBaars, and U. K. Mishra, "Power and linearity characteristics of GaN MISFETs on sapphire substrate," *IEEE Electron Device Lett.*, vol. 25, no. 2, pp. 55–57, Feb. 2004, doi: 10.1109/LED.2003.822668.

- [24] M. Ochiai, M. Akita, Y. Ohno, S. Kishimoto, K. Maezawa, and T. Mizutani, "AlGaN/GaN heterostructure metal-insulatorsemiconductor high-electron-mobility transistors with Si<sub>3</sub>N<sub>4</sub> gate insulator," *Jpn. J. Appl. Phys.*, vol. 42, no. 4B, pp. 2278–2280, Apr. 2003, doi: 10.1143/jjap.42.2278.

- [25] V. Joshi, A. Soni, S. P. Tiwari, and M. Shrivastava, "A comprehensive computational modeling approach for AlGaN/GaN HEMTs," *IEEE Trans. Nanotechnol.*, vol. 15, no. 6, pp. 947–955, Nov. 2016, doi: 10.1109/TNANO.2016.2615645.

- [26] V. Joshi, S. D. Gupta, R. R. Chaudhuri, and M. Shrivastava, "Physical insights into the impact of surface traps on breakdown characteristics of AlGaN/GaN HEMTs—Part I," *IEEE Trans. Electron Devices*, vol. 68, no. 1, pp. 72–79, Jan. 2021, doi: 10.1109/TED.2020.3034561.

- [27] V. Joshi, S. D. Gupta, R. R. Chaudhuri, and M. Shrivastava, "Interplay between surface and buffer traps in governing breakdown characteristics of AlGaN/GaN HEMTs—Part II," *IEEE Trans. Electron Devices*, vol. 68, no. 1, pp. 80–87, Jan. 2021, doi: 10.1109/TED.2020.3034562.

- [28] J. L. Lyons, A. Janotti, and C. G. Van de Walle, "Effects of carbon on the electrical and optical properties of InN, GaN, and AlN," *Phys. Rev. B, Condens. Matter*, vol. 89, no. 3, Jan. 2014, Art. no. 035204, doi: 10.1103/PhysRevB.89.035204.

- [29] J. L. Lyons, A. Janotti, and C. G. Van de Walle, "Carbon impurities and the yellow luminescence in GaN," *Appl. Phys. Lett.*, vol. 97, no. 15, Oct. 2010, Art. no. 152108, doi: 10.1063/1.3492841.