# Adaptive Dielectric Thin Film Transistors-A Self-Configuring Device for Low Power Electrostatic Discharge Protection

Prasenjit Bhattacharya<sup>®</sup>, *Student Member, IEEE*, Rajat Sinha, Bikash Kumar Thakur, Virendra Parab, Mayank Shrivastava<sup>®</sup>, *Senior Member, IEEE*, and Sanjiv Sambandan<sup>®</sup>

Abstract—Large area and flexible electronic systems are widely used in applications such as displays, image sensors, wearable electronics and energy harvesting systems. A key element in many of these systems is the electrostatic discharge protection circuit. The conventional protection circuit uses large aspect-ratio diode connected thin film transistors that offer a low resistance path to the surge current but also does the same to signals during normal system operation resulting in power loss. Here we describe as well as demonstrate the feasibility of a novel idea for electrostatic discharge protection involving an adaptive dielectric thin film transistor that self-configures itself to a low resistance state during an electrostatic discharge event and a high resistance state during normal operation without external control. This results in 1000-10000 times the power savings compared to diode connected TFTs.

*Index Terms*— Thin film transistors, electrostatic discharge, thin film circuits.

#### I. INTRODUCTION

THIN film transistor (TFT) based large area and flexible electronic systems require electrostatic discharge (ESD) protection [1]–[4]. An ESD event is a rapid transfer of finite charge between two systems resulting in a current surge that could damage the core circuit [5]. The charge source could be viewed as being located at the peripheral contact pad and an ESD protection circuit is placed at this location to shunt the surge current and protect the core circuit (Fig. 1(a)).

The conventional ESD protection circuit uses two, large-aspect ratio, diode connected TFTs in anti-parallel

Manuscript received November 6, 2019; revised November 25, 2019; accepted November 26, 2019. Date of publication November 29, 2019; date of current version December 27, 2019. This work was supported by Engineering and Physical Sciences Research Council Grant No. RG92121, Department of Science and Technology Grant No. 7969 Imprint and Department of Biotechnology-Cambridge Lectureship. The review of this letter was arranged by Editor H. Gossner. (*Corresponding author: Sanjiv Sambandan.*)

P. Bhattacharya and V. Parab are with the Department of Instrumentation and Applied Physics, Indian Institute of Science, Bengaluru 560012, India

R. Sinha and M. Shrivastava are with the Department of Electronic System Engineering, Indian Institute of Science, Bengaluru 560012, India

B. K. Thakur is with Qualcomm, Bengaluru 560066, India

S. Sambandan is with the Department of Engineering, University of Cambridge, Cambridge CB3 0FF, U.K., with the Department of Instrumentation and Applied Physics, Indian Institute of Science, Bengaluru 560012, India, and also with the Department of Electronic Systems Engineering, Indian Institute of Science, Bengaluru 560012, India (e-mail: ss698@cam.ac.uk; sanjiv@iisc.ac.in).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2019.2956838

Conventional TFT ESD event ESD curren Input/ Outpu otectio pad device (a) (b) Adaptive dielectric thin film transistor (adTFT) Mas electrode ( Bottom dielectri Masking semiconducto 4-terminal 3-terminal 2-termina adTFT adTFT adTFT (c)

Fig. 1. (a) ESD protection. (b) Conventional TFT. (c) Adaptive dielectric TFT (adTFT).

configuration [6]–[12]. This circuit offers a low resistance path to the surge current but also does the same to signals during normal system operation resulting in power loss [10], [11]. Additional circuits are required to keep the protection circuit turned off during normal operation [10], [13]–[16].

In this work we discuss the feasibility of using a new device architecture called the 'adaptive dielectric thin film transistor (adTFT)' for ESD protection. The adTFT self-configures itself to a low resistance state during an ESD event and a high resistance state during normal operation without external control resulting in power savings by a factor of  $10^3 - 10^4$  compared to the conventional diode connected TFT while showing similar ESD robustness. The adTFT therefore condenses into a single device all the circuit complexity required to achieve this performance thereby saving routing complexity and layout area.

## II. DESIGN AND OPERATION OF THE ADTFT

The device architecture and circuit symbol of the conventional TFT and adTFT are shown in Fig. 1(b) and Fig. 1(c), respectively. Like a conventional TFT, the adTFT has a gate (G), source (S) and drain (D) electrode with a source/drain-gate overlap. The semiconductor between source and drain, henceforth called the 'primary semiconductor' for clarity, conducts the adTFT drain-source current. However, unlike the conventional TFT, the adTFT has a composite dielectric with a thin semiconductor film sandwiched between two insulating films resulting in an insulator-semiconductorinsulator stack. This sandwiched semiconducting film, referred to as the 'masking semiconductor', is connected to a reservoir of charge via the 'mask electrode (M)'. Due to an underlap between the mask electrode and gate, channel formation in

0741-3106 © 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

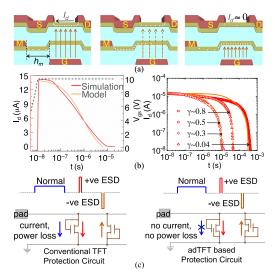

Fig. 2. (a) Operation of the adTFT. (b) Model versus simulation. For models,  $k \approx 2 \times 10^{-19} \text{ A.cm}^3/\text{V}^2$ ,  $\lambda \approx 5.97 \times 10^5 \text{ (Vs)}^{-1}$ . (c) ESD protection circuit with conventional TFTs and adTFTs. During normal operation, the adTFT based protection circuit does not consume power.

the primary semiconductor is faster than in the masking semiconductor. Two 2-terminal adTFTs (diode connected configuration) are used anti-parallelly to construct an ESD protection circuit.

The operation of the 3-terminal adTFT is best described by considering a step input in the gate-source voltage,  $V_{gs}$ . Fig. 2(a) illustrates the expected device behavior. As  $V_{gs}$ increases, carriers injected from the source result in channel formation in the primary semiconductor and a significant  $I_d$ . The masking electrode also responds to the increase in  $V_{gs}$ by injecting carriers into the masking semiconductor. Due to the gate-source overlap and the gate-mask underlap of length  $h_m$ , the former process is faster. However with enough time, a channel eventually forms in the masking semiconductor and shields the primary semiconductor from the gate field resulting in a decrease in  $I_d$  to leakage levels.

The dynamics of  $I_d$  can be modeled by treating the masking semiconductor as a zone of trapped charge that influences the threshold voltage,  $V_T$ . The mask current that charges the masking semiconductor is space charge limited [17]. The dynamic response of  $V_T$  to the step input in  $V_{gs}$  in the time interval  $0 < t \le (V_{T0}^{-1} - V_{gs}^{-1})/(\gamma (1 - \gamma)^2 \lambda)$  can be shown to be  $V_T(t) \approx V_{T0} + V_{gs} - \left(V_{gs}^{-1} + \gamma (1-\gamma)^2 \lambda t\right)^{-1}$ . Here,  $\lambda = k/(C_i(L+2L_{ov})Wh_m^3), V_{T0}$  is the threshold voltage when the masking semiconductor is not charged,  $C_i$  the gate dielectric capacitance per unit area, W the channel width, L the channel length,  $L_{ov}$  the source/drain-gate overlap length and k a fitting parameter defining the mask current (units  $A.cm^3/V^2$ ). Since the coefficient  $\lambda \propto h_m^{-3}$ , decreasing the gate-mask underlap length,  $h_m$ , results in rapid screening and reduction in  $I_d$  with time. The parameter  $0 < \gamma < 1$  defines the location of the masking semiconductor in the dielectric stack. When  $\gamma \rightarrow 0$ , the masking semiconductor is located at the gate interface and has a high initial potential resulting in a large mask current. However, its impact on  $V_T$  is low due to its location. When  $\gamma \rightarrow 1$ , the masking semiconductor is located at the primary semiconductor interface with a low initial potential and therefore a low mask current while having a high impact on  $V_T$ . The maximum screening rate is therefore

Fig. 3. (a) SEM cross-section of the adTFT (b) Micrograph of the single sided mask adTFT (c) Micrograph of the surround mask adTFT.

expected when the masking semiconductor lies close to the middle, i.e. when  $0.3 \le \gamma \le 0.5$ . Fig. 2(b) compares the  $I_d$  calculated using the models with TCAD simulations.

Based on the above discussion, it is seen that the adTFT can be used as a power efficient ESD protection device (Fig. 2(c)). During an ESD event, the rapid increase in  $V_{gs}$  resulting in a large  $I_d$  would shunt the surge current. During normal operation, the masking semiconductor would have sufficient time for channel formation thereby making  $I_d$  negligible and saving power.

## **III. FABRICATION**

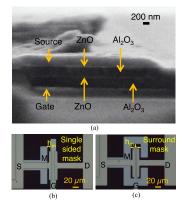

The gate electrode was e-beam evaporated 75 nm Al on the Corning glass substrate. The adaptive dielectric stack was composed of 235 nm Al<sub>2</sub>O<sub>3</sub> (top dielectric)-30 nm ZnO (masking semiconductor)-235 nm Al<sub>2</sub>O<sub>3</sub> (bottom dielectric). The bottom and top dielectric were formed by e-beam evaporating Al<sub>2</sub>O<sub>3</sub> at  $7.5 \times 10^{-2}$  mTorr with 4 sccm O<sub>2</sub> gas flow followed by annealing at 175°C for 30 mins. The masking semiconductor was rf sputtered ZnO at 2 W/cm<sup>2</sup> in Ar:O<sub>2</sub> (9:1) environment at 7 mTorr. The mask electrode was an e-beam evaporated stack of 10 nm Ti and 100 nm Al. The primary semiconductor (35 nm ZnO) was deposited by a process similar to the masking semiconductor. The source/drain (5  $\mu$ m gate overlap) were an e-beam evaporated stack of 10 nm Ti and 100 nm Al.

Fig. 3(a) shows the cross-section SEM of the adTFT at the gate-source overlap region. Two types of adTFTs were fabricated - 'single sided mask' adTFT with the masking electrode on one side of the device (Fig. 3(b)) and the 'surround mask' adTFT with the masking electrode surrounding the device (Fig. 3(c)). The experimental control was an adTFT without the masking electrode. These devices behaved similar to conventional TFTs and are labeled as such.

#### **IV. RESULTS AND DISCUSSIONS**

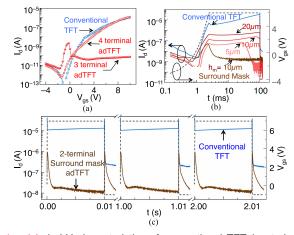

The dc current-voltage (I-V) characteristics of the conventional TFT (control), the 4-terminal adTFT (with the mask electrode open or floating) and the 3-terminal adTFT ( $W = 200 \ \mu m$ ,  $L = 10 \ \mu m$  and  $h_m = 10 \ \mu m$ ) were measured with  $V_{ds} = 1$  V and  $V_{gs}$  swept in 0.1 V steps at  $\approx 0.47$  V/s. As seen in Fig. 4(a), the 4-terminal adTFT behaved similar to the conventional TFT due to the floating mask electrode whereas the 3-terminal adTFT behaved as predicted by the physics described in Fig. 2(a).

The dynamic performance of the 3-terminal single sided mask adTFT ( $W = 300 \ \mu m$ ,  $L = 10 \ \mu m$ ,

Fig. 4. (a) dc I-V characteristics of conventional TFT (control, blue) and adTFT (red). (b) Pulsed I-V characteristics of the conventional TFT (control, blue), single sided mask adTFTs with different  $h_m$  (in varying shades of red) and surround mask adTFT (brown). (c) Transient response of 2-terminal (diode connected) surround mask adTFT to a periodic gate pulse.

Fig. 5. (a) TLP I-V characteristics (b) adTFTs after failure (c) Power to thermal breakdown in conventional and adTFTs.

$h_m = \{5, 10, 20\} \ \mu$ m) and 3-terminal surround mask adTFT ( $W = 300 \ \mu$ m,  $L = 10 \ \mu$ m,  $h_m = 10 \ \mu$ m) in response to a single gate pulse (-4 V to 6 V, rise/fall time of 2.5 ms, pulse width 100 ms) is shown in Fig. 4(b). The single sided mask adTFT showed a lower masking time (i.e. quicker screening) with decreasing  $h_m$ , as predicted by the physics. The surround mask architecture showed a lower masking time compared to the single sided mask architecture due to carrier injection from multiple sides. The surround mask architecture would therefore improve power savings if normal system operation constituted pulsed line voltages (e.g. displays) as opposed to constant voltages.

Fig. 4(c) shows the response of the diode connected surround mask adTFT and a diode connected conventional TFT to a periodic gate signal (10 ms pulse width, 50  $\mu$ s rise/fall time). It is noted that the peak  $I_d \approx 1 \ \mu$ A is smaller than typical ESD currents (100 mA-1 A). This is due to the slow rising pulse (~ 50  $\mu$ s) where the shielding action diminishes  $I_d$ . An ESD event would be faster and  $I_d$  higher. Such conditions were tested via transmission line pulse (TLP) measurements (Fig. 5) [18]–[20].

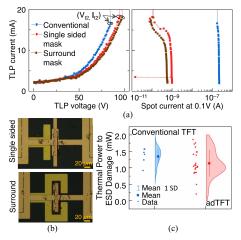

Fig. 5 shows TLP measurements with the conventional TFT and adTFTs. Diode connected devices were subjected to a

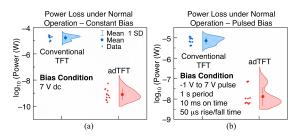

Fig. 6. Power loss in conventional TFTs and adTFTs during normal operation. Line voltage during normal operation being (a) dc (b) pulsed.

train of increasing voltage pulses (1 V increment, 100 ns pulse width,  $\sim 1$  s period,  $\sim 10$  ns rise/fall time) and the average  $I_d$  was measured during the pulse on period. After each pulse, dc spot current measurements at  $V_{ds} = 0.1$  V monitored device degradation. Fig. 5(a) compares the TLP I-V characteristics for conventional TFT, single sided mask adTFT and surround mask adTFT (all devices  $W = 200 \ \mu m$ ,  $L = 5 \ \mu \text{m}, \ h_m = 10 \ \mu \text{m}$ ). Spot currents in adTFTs were low due to the shielding effect. All devices failed due to self heating with the source/drain thermally damaged and mask electrode not damaged (Fig. 5(b)). The failure point,  $(V_{t2}, I_{t2})$ , was observed to be (84.7 V, 16.6 mA), (94.7 V, 18.2 mA) and (97.2 V, 18.1 mA) with the power to thermal breakdown,  $V_{t2}I_{t2}$ , being 1.41 W, 1.72 W and 1.75 W, for the conventional TFT, single sided mask adTFT and the surround mask adTFT, respectively. ZnO based adTFTs showed a surge current shunting capacity of 0.08 mA/ $\mu$ m for  $L = 5 \ \mu$ m.

Fig. 5(c) and 6 show the statistics of device performance and highlight the primary advantage of the adTFT. Diode connected adTFTs showed similar ESD protection ability compared to the diode connected conventional TFTs as observed from the power to thermal breakdown (Fig. 5(c)). Since  $V_{t2} \propto L$  and  $I_{t2} \propto W$ , the power to thermal breakdown of devices with different geometries were compared after normalizing with respect to WL. Despite similar ESD performance, diode connected adTFTs show more power saving during normal system operation as compared to diode connected conventional TFTs. To compare the power consumption of devices with different geometries, results were normalized with respect to W/L. Depending on whether normal operation consisted of dc (7 V dc) or pulsed operation (-1 V to 7 V pulse, 1 s period, 10 ms on time, 50  $\mu$ s rise/fall time), the adTFT based protection circuit consumed  $\approx 10^4$  and  $\approx 10^3$  times less power compared to a conventional TFT based protection circuit, respectively (Fig. 6(a) and Fig. 6(b)). Since the power consumption in the conventional TFTs developed in this work is equivalent to other reports with metal oxide semiconductor TFTs [11], it is expected that the adTFT based protection circuits would have similar impact in terms of power savings across these materials. Finally, the layout area for conventional TFT based protection circuits sclaes as  $\sim 2W(L + 2L_{ov})$ , whereas the adTFT based protection circuit has a layout area that scales as  $\sim 2W(L + 2L_{op} + h_m)$ .

## V. CONCLUSION

This work discussed the architecture and physics of a new device called the adaptive dielectric thin film transistor (adTFT). When used for ESD protection, the adTFT permitted a large drain current during the rapid ESD event thereby shunting the current surge and drew little current during normal operation thereby saving power.

#### REFERENCES

- N. Golo-Tosic, A. J. S. M. Jenneboer, and A. J. Mouthaan, "Dealing with electrostatic discharge in a captive fingerprint sensor fabricated in amorphous silicon thin film technology," in *Proc. SESENS*. Utrecht, The Netherlands: STW, 2002, pp. 616–621.

- [2] S.-C. Lee, B.-C. Jeon, K.-C. Moon, M.-C. Lee, and M.-K. Han, "P-4: Electro static discharge effects on polysilicon TFTs for AMLCD," in *SID Symp. Dig. Tech. Papers*, vol. 33, no. 1, pp. 212–215, May 2002.

- [3] M.-D. Ker, T.-K. Tseng, A. Shih, S.-C. Yang, and Y.-M. Tsai, "51.3: Successful electrostatic discharge protection design for LTPS circuits integrated on panel," in *SID Symp. Dig. Tech. Papers*, vol. 34, no. 1, pp. 1400–1403, May 2003.

- [4] H. Fuketa, K. Yoshioka, T. Yokota, W. Yukita, M. Koizumi, M. Sekino, T. Sekitani, M. Takamiya, T. Someya, and T. Sakurai, "30.3 organictransistor-based 2kV ESD-tolerant flexible wet sensor sheet for biomedical applications with wireless power and data transmission using 13.56MHz magnetic resonance," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 490–491.

- [5] J. E. Vinson and J. J. Liou, "Electrostatic discharge in semiconductor devices: An overview," *Proc. IEEE*, vol. 86, no. 2, pp. 399–420, Feb. 1998.

- [6] C.-K. Deng and M.-D. Ker, "ESD robustness of thin-film devices with different layout structures in LTPS technology," *Microelectron. Rel.*, vol. 46, no. 12, pp. 2067–2073, Dec. 2006.

- [7] M.-D. Ker, J.-Y. Chuang, C.-K. Deng, C.-H. Kuo, C.-H. Li, M.-S. Lai, C.-W. Wang, and C.-T. Liu, "On-panel electrostatic discharge (ESD) protection design with thin-film transistor in LTPS process," in *Proc. Asia Display*, vol. 1, 2007, p. 551.

- [8] Y.-H. Tai, H.-L. Chiu, and L.-S. Chou, "Test and analysis of the ESD robustness for the diode-connected a-IGZO thin film transistors," *J. Display Technol.*, vol. 9, no. 8, pp. 613–618, Aug. 2013.

- [9] M. Scholz, S. Steudel, K. Myny, S. Chen, R. Boschke, G. Hellings, and D. Linten, "ESD protection design in a-IGZO TFT technologies," in *Proc. 38th Electr. Overstress/Electrostatic Discharge Symp. (EOS/ESD)*, Sep. 2016, pp. 1–7.

- [10] N. Wang, S.-H. Chen, G. Hellings, K. Myny, S. Steudel, M. Scholz, R. Boschke, D. Linten, and G. Groeseneken, "ESD characterisation of a-IGZO TFTs on si and foil substrates," in *Proc.* 47th Eur. Solid-State Device Res. Conf. (ESSDERC), Sep. 2017, pp. 276–279.

- [11] M. Simicic, G. Hellings, S.-H. Chen, K. Myny, and D. Linten, "ESD study on a-IGZO TFT device architectures," in *Proc. 40th Elect. Overstress/Electrostatic Discharge Symp. (EOS/ESD)*, Sep. 2018, pp. 1–7.

- [12] R. Sinha, P. Bhattacharya, I. E. T. Iben, S. Sambandan, and M. Shrivastava, "ESD reliability study of a-Si:H thin-film transistor technology: Physical insights and technological implications," *IEEE Trans. Electron Devices*, vol. 66, no. 6, pp. 2624–2630, Jun. 2019.

- [13] H. Watanabe and T. Inada, "Display device with electrostatic discharge protection circuitry," U.S. Patent 7453 420, Nov. 18, 2008.

- [14] D. Liye and Z. Wu, "Electro-static discharge protection circuit and method for driving the same and display panel," U.S. Patent 9013846, Apr. 21, 2015,

- [15] Z. Huang, "ESD protection device of touch panel," U.S. Patent 9520715, Dec. 13, 2016.

- [16] J. R. Hector, N. C. Bird, S. C. Deane, T. Ohmoto, and H. Watanabe, "Electrostatic discharge protection for pixellated electronic device," U.S. Patent 6 696 701. Feb. 24, 2004,

- [17] P. Mark and W. Helfrich, "Space-charge-limited currents in organic crystals," J. Appl. Phys., vol. 33, no. 1, pp. 205–215, 1962.

- [18] H. Wolf, H. Gieser, and W. Wilkening, "Analyzing the switching behavior of ESD-protection transistors by very fast transmission line pulsing," *J. Electrostatics*, vol. 49, nos. 3–4, pp. 111–127, Aug. 2000.

- [19] H. Hyatt, J. Harris, A. Alonzo, and P. Bellew, "TLP measurements for verification of ESD protection device response," *IEEE Trans. Electron. Packag. Manuf.*, vol. 24, no. 2, pp. 90–98, Apr. 2001.

- [20] J. E. Barth, K. Verhaege, L. G. Henry, and J. Richner, "TLP calibration, correlation, standards, and new techniques," *IEEE Trans. Electron. Packag. Manuf.*, vol. 24, no. 2, pp. 99–108, Apr. 2001.