Prof. Mayank Shrivastava

Professor & Chair

Department of Electronic Systems Engineering

Indian Institute of Science Bangalore, 560012

Co-Founder, AGNIT Semiconductors Pvt. Ltd.

Investigator, Gallium Nitride EcoSystem Enabling Center (GaN Fab)

E-mail: mayank@iisc.ac.in

Web: http://mayank.dese.iisc.ac.in/

Contact: +91-80-2293-2732 / +91 96863 40309

Biography

Prof. Mayank Shrivastava is a Full Professor at the Indian Institute of Science, Bangalore, and co-founder of AGNIT Semiconductors Pvt. Ltd., which is a deep-tech start-up in the semiconductor space. He is also instrumental in setting up Gallium Nitride prototyping Fab worth 347 Cr. He received his Ph.D. degree from the Indian Institute of Technology Bombay. For his Ph.D. work, he received Excellence in Research award and the Industrial Impact award from IIT Bombay in the year 2010. He joined the Indian Institute of Science as a faculty member in the year 2013. Prior to joining IISc, he held positions in Infineon Technologies, Munich, Germany; Infineon Technologies, East Fishkill, USA; IBM Microelectronics, Burlington, USA; Intel Mobile Communications, Hopewell Junction, USA; Intel Corp, Mobile and Communications Group, Munich, Germany, between 2009 and 2013.

Prof Shrivastava’s work has resulted in over 270 peer-reviewed international publications of high repute (over 60 of these papers are in IRPS and IEDM, the two most prestigious conferences of IEEE EDS where most of the breakthroughs are reported, and around 100 are in journals such as IEEE Transactions) and over 60 patents. Most of these patents are either licensed by semiconductor companies or are in use in their products. He has guided/trained over 40 PhD students, over a dozen postdoc fellows, and over 100 master’s students and research staff. He is among the first recipients of the Indian section of the American TR35 award (2010) and the first Indian to receive IEEE EDS Early Career Award (2015). He is also an Editor of IEEE Transactions on Electron Devices and IEEE Transactions on Materials for Electron Devices. Besides, he is an IEEE Electron Device’s Society (EDS) Distinguished Lecturer and an elected member of the IEEE EDS Board of Governors. He has also served on the technical and executive committees of over a dozen international conferences around the world.

Overall, he is a recipient of over 25 national and international awards, recognitions, and honors of high repute, such as the prestigious DST Swarnjayanti Fellowship (2021), Abdul Kalam Technology Innovation National Fellowship from INAE-SERB (2021), and the VASVIK award (2021), the National Academy of Sciences, India, (NASI) Young Scientist Platinum Jubilee Award – 2018; Indian National Academy of Science (INSA) Young Scientist Award – 2018; Indian National Academy of Engineering (INAE) Innovator Entrepreneur Award 2018 (Special commendation); Indian National Academy of Engineering (INAE) Young Engineer Award – 2017; INAE Young Associate (since 2017); Indian Academy of Sciences (IASc), Young Associate, 2018 – 2023; Ministry of Electronics & Information Technology (MeitY), Young Faculty Fellowship. Besides, he received best paper awards from several international conferences like Intel Corporation Asia academic forum, VLSI design Conference and EOSESD Symposium.

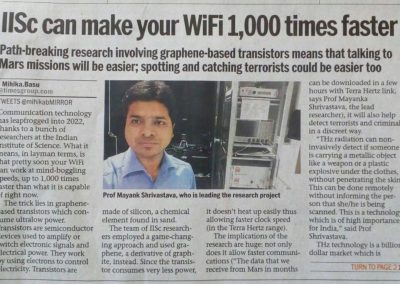

Prof Shrivastava broadly works on applications of emerging semiconductor materials like Gallium Nitride (GaN), atomically thin two-dimensional materials like Graphene and TMDCs, in electronic and electro-optic devices working closer to its fundamental limits. Besides, his group also works closely with semiconductor industries on developing novel device concepts for advanced CMOS and automotive nodes.

Work Experience

- Professor, Department of Electronic Systems Engineering, Indian Institute of Science Bangalore (June 2024 – Present).

- Associate Professor, Department of Electronic Systems Engineering, Indian Institute of Science Bangalore (June 2019 – June 2024).

- Assistant Professor, Department of Electronic Systems Engineering, Indian Institute of Science Bangalore (September 2013 – May 2019).

- Staff Engineer: Intel Corp. (MCG), Munich, Germany (April. 2013 – August 2013).

- Senior Engineer: Intel Corp. (MCG), Munich, Germany (Sep. 2011 – March 2013).

- Senior Engineer: Infineon Technologies, USA (Sep 2010 to Jan 2011) and Intel Corp. (MCG), USA, (Feb 2011 to Sep 2011).

- Visiting Scholar: Infineon Technologies, Munich, Germany. April 2008 to Oct 2008 & May 2010 to July 2010.

Entrepreneurial Experience

- Co-Founder, AGNIT Semiconductors Pvt. Ltd.

- Investigator, Gallium Nitride Ecosystem Enabling Centre and Incubator (GEECI)

Contributions in Leadership Roles

- VAIBAHV Summit: This was the Indian Prime Minister’s effort to bring the Indian Diaspora under one roof. Prof. Shrivastava led the electronics/semiconductor vertical and could get the majority of the Indian diaspora under one roof to discuss/brainstorm various topics of collaborative interest. The proceedings ran for 3 weeks, which resulted in a 300-page report and a key policy document submitted to the Prime Minister’s office. This policy document has also helped shape the Indian Semiconductor Strategies and several new programs under the VAIBHAV initiative.

- Gallium Nitride Fab: Prof. Shrivastava is instrumental in setting up Gallium Nitride Fab in India. This prototyping Fab would not only develop commercial equivalent GaN devices but would also support start-ups in the GaN technology arena.

- National Initiative on 2D Material-Based Future Technology Center: Prof. Shrivastava is driving this national effort: https://www.psa.gov.in/article/india-embarks-2d-materials-based-future-technologies/3595, which involved collaborating/interacting with several faculty members in IISc, over two dozen faculty members abroad, around 100 researchers from various leading institutions in India, around 15 industries and over 40 scientists from 11 strategic/govt. labs/policy offices while navigating towards an agreed-by-all roadmap for the proposed 2D center.

- IISc Master’s Program in Microelectronics & VLSI Design: Prof. Shrivastava was instrumental in transitioning it into the most sought-after master’s program in India for Electrical Engineering graduates and GATE toppers with a vibrant participation of Industry.

- Popularizing Research Done in India: Prof. Shrivastava has been actively popularizing research work done in India and the potential that exists in India at many forums including Industries and academia around the world. His talk and writing on “Why Ph.D. – Breaking the Myths and Misconceptions” and his writings/talks on “Brain Drain” are quite well-received.

- IEEE Electron Device Society – Bangalore Chapter Chair: In his leadership, it not only became one of the most active EDS chapters but also attained a very high level of financial stability and independence.

- International Conference on Emerging Electronics (ICEE): Prof. Shrivastava has been serving in the IEEE ICEE’s leadership/executive committee since 2018. In 2022 he served as the general chair. In this role, he led a team of over 170 experts (Industry and Academia) from around the world. His team transformed ICEE into one of the largest IEEE Electron Devices conferences in the world with participation from around the world having a significant fraction from leading semiconductor industries. The conference also resulted in over 300 outstanding scientific contributions, many policy suggestions, and a roadmap for the world to progress further in semiconductor technologies.

- India ESD Forum: Until the Year 2023 there was barely any ESD knowledge/awareness in India. ESD is a key field related to semiconductor reliability. He started what is now called the India ESD Forum. This enabled connecting semiconductor industry professionals and systematically grew the community and knowledgebase from less than 5 (ten years back) to over 300 engineers in the industry today.

- Research Facility: He has built a one of its kind semiconductor and quantum device characterization and modelling facility in IISc.

- National and International Advisory Committees: Prof. Shrivastava has also served in several national and international technical advisory committees, review committees, etc.

Key Industry Interactions

- Nexperia, UK: To explore novel device and material concepts for advanced power MOSFETs to push the fundamental ON-Resistance vs. breakdown voltage limit.

- Intel (Germany): To explore novel ESD device designs/architectures in FinFET nodes. This project resulted in 5 US patents (in use by Intel) disclosing several novel ESD device concepts in FinFET nodes. Besides, it resulted in several high-quality publications, one best paper award, and two PhD students.

- Intel (India): To explore the heat-spreading ability of graphene and the role of defects/grain boundaries in thermal transport across graphene. Subsequently, use the physical insights to develop efficient heat-spreading solutions using graphene and other 2D materials. This engagement is supporting one PhD student.

- Texas Instruments (USA): In the first phase (Year 2017-20) of the project the engagement was to explore the physics behind current filamentation and power scalability issues in LDMOS-SCR devices for advanced automotive nodes. In the second phase (The year 2020-23), we explored power-to-fail scalability issues in several device architectures in automotive nodes under IEC-like stress conditions. This project resulted in ESD robust LDMOS-SCR devices and several IEC robust ESD protection devices that are in use in TI’s products. Some of the TI products that were earlier plagued by early failure under system-level stress conditions have passed reliability qualification after adopting the design modifications proposed in this project. Besides, it resulted in several high-quality publications and two PhD students. Both the students were acquired later by TI. Phase three (The year 2023-26) has continued on the same thread while also modeling the complex failure dynamics under system ESD stress conditions. This engagement so far has supported four PhD students.

- Alpha & Omega Semiconductors (USA): This engagement was with the TVS group. We were chartered to explore/develop a range of TVS protection devices (4 unique products), which must be better than the devices available in the market while meeting a target datasheet. This project also graduated four postdocs, one hired by Nexperia (a leading semiconductor company in the UK) to lead the TVS group in the UK, and two others moved to AOS to lead the TVS development within AOS.

- Alpha & Omega Semiconductors (USA): Another engagement is going to be with the SiC group, where we are chartered to explore novel device designs (both lateral gate and trench gate concepts) to beat the current SiC state of the art.

- Samsung (Korea): The project is to explore and invent novel ways to protect ESD phenomena in their advanced CMOS node, particularly for ultra-fast IO applications, where the need is to significantly suppress the parasitic capacitance and boost failure current per unit area. Besides, we are also building scalable models for SCR-based ESD protection devices.

- Samsung (India): Funded to build a Quantum Technology Lab.

- Keysight (India): Funded to build a Quantum Technology Lab.

- A Leading Semiconductor Company (Name Can’t be Disclosed): Technical Advisory Board of the company.

- Synopsys (India & USA): Funded resources worth USD 75M to start a new program titled: India Semiconductor Workforce Development Program.

- Semiconductor Complex Limited (SCL, India): Their base process was licensed from another company, which was limited to 1.8V core devices. To develop any SoC product one would need high voltage (LDMOS) devices of 10V, 14V, 40V, and 80V classes, and ESD protection devices. We developed the entire range of LDMOS devices for SCL, ported the processes, and qualified it for it to eventually appear in an extended PDK. More details are disclosed here: https://auto.economictimes.indiatimes.com/news/auto-components/iisc-technology-can-address-automotive-chip-shortage/89987058

Funding and Sponsors

|

So. No. |

Project Title |

Agency |

Value in Rs. (Lacs) |

Duration |

PI/Co-PI/Investigator |

|

1 |

Institute Seed Grant for the Establishment of Advance Nanoelectronics Device & Circuit Research Laboratory |

IISc |

34 |

Oct 2013 – Sep 2014 |

PI |

|

2 |

Demonstration of Graphene based RF Transistors |

DRDO (SSPL) |

10 |

June 2014 – Oct. 2014 |

PI |

|

3 |

Exploration of Carrier Transport and Contact Resistance Behaviours in Carbon Nanotube and Graphene Devices Using Nanosecond Time Scale Charge Bust |

DST (SERB) |

51 |

July 2014 – June 2017 |

PI |

|

4 |

Investigation on GaN devices for power electronic switching applications and design and development of a high frequency GaN convertors topology |

NaMPET Phase-II |

191 |

Oct. 2014 – March 2017 |

Co-PI |

|

5 |

Advance Nanoscale Characterization Facility |

IISc |

110 |

Jan 2015 – Sep 2015 |

PI |

|

6 |

ESD Reliability of sub-14nm node technologies |

Intel, Germany |

150K USD |

Dec 2015 – Nov. 2018 |

PI |

|

7 |

12th Plan Grant to Develop Laboratory Space |

IISc |

5 |

Sep 2016 – March 2017 |

PI |

|

8 |

Technology Development for 600V Normally – OFF Gallium Nitride Transistor for Reliable Power Electronic Systems |

DST (TSDP) |

1028 |

May 2016 – August 2020 |

PI |

|

9 |

Graphene Based THz Transistor Technology |

DRDO (ERIPR) |

500 |

March 2017 – March 2023 |

PI |

|

10 |

High Voltage & ESD Device Development & Enablement in SCL’s 180nm CMOS Technology |

IMPRINT |

300 |

March 2017 – March 2021 |

PI |

|

11 |

Detailed Project Report on GaN Foundry |

DeitY |

60 |

March 2016 – Sep. 2016 |

Co-PI |

|

12 |

Power-scalability of Advance Semiconductor Devices from ESD time domain to DC |

Texas Instruments (USA) |

165K USD |

Oct 2017 – Sep 2020 |

PI |

|

13 |

2D Material Based Transistor Technology |

NNeTRA program of MeitY |

150 (sub-project) |

April 2018 – March 2022 |

Co-PI |

|

14. |

Exploratory Project under IOE |

IISc/MHRD |

200 |

August 2019 – March 2020 |

PI |

|

15. |

Advance Nanoscale Characterization Facility (II) |

IISc (MHRD) |

150 |

March 2018 – Sep. 2018 |

PI |

|

16. |

HV ESD Protections Design for On-Chip IEC ESD |

TI, USA |

210K USD |

Oct. 2020 – Sep. 2023 |

PI |

|

17. |

Development of New TVS Product and Technology |

AOS, USA |

450K USD |

Nov. 2020 – Oct. 2023 |

PI |

|

18. |

Performance and Reliability Co-Design of e-mode GaN HEMTs |

DST, SERB (CRG) |

66 |

September 2021 – August. 2024 |

PI |

|

19. |

A Novel Memory Synapse Technology for Neuromorphic Computing |

DST, SERB |

380 |

March 2022 – Feb 2027 |

PI |

|

20. |

Development of On-board (In-Vehicle) Fast DC Chargers Using High-Speed GaN HEMTs for Two-Wheeler (2W) Electric Vehicles |

MeitY |

450 |

April 2022 – March 2024 |

PI |

|

21. |

Development of Rugged 30A/650V e-mode Power HEMT Technology and Fast 1kW DC Charger using the in-house Developed Power HEMT |

DST, AMT |

1150 |

April 2022 – March 2025 |

PI |

|

22. |

GaN-Based THz Devices (Abdul Kalam Fellowship) |

INAE |

75 |

Oct. 2021 – Sep. 2026 |

PI |

|

23. |

Industry Grants For Microelectronics Lab |

Several Industries |

75 |

2019 – 2022 |

PI |

|

24. |

High-Speed ESD Protection Design in Advanced CMOS Nodes |

Samsung |

360 |

Sep. 2022 – Sep. 2025 |

PI |

|

25. |

Performance-reliability Co-design Approach for High-performance and High Reliability Normally OFF Vertical β-Ga2O3 Field Effect Transistors (FETs) |

DST SERB |

60 |

Jan 2023 – Dec 2025 |

PI |

|

26. |

Graphene-Based Heat Spreader with Thermal Conductivity Crossing 3000 W/m-K for Next Generation Electronic Systems |

Intel |

80 |

Oct. 2023 – Sep. 2025 |

PI |

|

27. |

Capital Support to Develop Quantum Technology Lab |

Samsung |

300 |

Sep. 2023 – March 2024 |

PI |

|

28. |

Capital Support to Develop Quantum Technology Lab |

Keysight |

40 |

Jan. 2023 – March 2023 |

PI |

|

29. |

Explorative Investigations Related to IEC Stress in Automotive Technologies |

Texas Instruments, USA |

420K USD |

Jan 2024 – Dec 2027 |

PI |

|

30. |

Power Semiconductor Device Roadmap |

Nexperia |

33K Euro |

April 2024 – March 2025 |

PI |

|

31. |

Capital Support to Develop Advanced HPC Facility |

Samsung |

600 |

Oct. 2024 – Sep. 2026 |

PI |

|

32. |

Record Low Ron Performance LDMOS Approaches & Predictive Reliability Modeling |

Nexperia |

900K USD |

1st April 2025 – 31st March 2028 |

PI |

|

33. |

Capital Support to Advance the Quantum Technology Lab |

Samsung |

300 |

August 2025 – March 2026 |

PI |

|

Total Sanctioned Funding till July 2025 |

~93 |

~11.5M USD* |

|||

*This doesn’t include the $75M funding received for setting up a prototyping GaN Foundry and $75M worth of computational resources received from Synopsys.

Facility

Research Facility in MSDLab

This is a ~40 Crore worth facility. The unique capabilities of this facility are being extensively utilized, not just by PhD students in MSDLab, but also by staff and students from several other departments. In general, this facility has helped develop several technologies such as graphene and 2D materials technology, high power Gallium Nitride technology, organic electronics and Si based power technology. The users can independently handle the tool post a systematic training.

1. Manual Probe Station

Lab has 3 manual probe stations. The tool allows holding and probing samples of 1cm size to 8-inch wafers. The probe station houses a high-end microscope with magnification up-to 1000, which allows probing nano-meter sized devices for DC and RF tests at temperatures between 300K to 500K. Besides, its capable of measuring ultra-low currents, as well as very high currents and voltages. The vibration free table with pneumatic isolation using a low noise air compressor allows high precision probing of the devices.

2. Semi-automatic Probe Station

It enables automatic DC and RF device characterization (up to 110 GHz), wafer-level reliability, e-test, modelling, or yield analysis. It is equipped with probe station control software to automate the measure 1000s of devices with a single click.

3. Range of Wafer Level Electrical Characterization Equipment

The facility has the following electrical characterization tools.

|

Equipment Type |

Make |

Model |

Specification |

|

SMU (4 Nos) |

Keithley 2400 |

Keithley 2400 |

General purpose SMU (100V, 1A) |

|

SMU (2 Nos) |

Dual Channel SMU |

Keithley 2635B |

Single Channel SMU capable of 1A DC (10A Pulse), 200V. |

|

SMU |

Dual Channel SMU |

Keithley 2636B |

Dual Channel SMU capable of 1A DC (10A Pulse), 200V |

|

SMU |

Dual Channel SMU |

Keysight |

Dual Channel SMU capable of 1A DC, 200V |

|

HC SMU (2 Nos) |

High Current SMU |

Keithley 2651A |

High Current SMU (Upto 50A in pulsed mode, 20A in DC mode) |

|

HV SMU (7 Nos) |

High Voltage SMU |

Keithley 2657A |

High Voltage SMU (Upto 3kV) |

|

CV Meter |

CVU |

Keithley PCT-CVU |

High voltage capacitance measurements |

|

Switching Matrix |

Switching Matrix |

Keithley 707B |

Six-slot semiconductor switch mainframe (8 input and 36 output ports) |

|

High Power interface panel |

Panel |

Keithley 8020 |

Interface between the Parametric Curve Tracer (PCT), SMUs, probe station and test fixtures for wafer level high power measurements. |

|

Parametric Curve Tracer (2 Nos) |

4200 |

4200A-SCS |

Parametric curve tracer with automation capability and switching matric for semiconductor device characterization. It consists of 6 medium power SMU, 1 CVU and 2 pulse measurement units. |

|

FFT Spectrum Analyzer |

SR760 |

SR760 |

Single-channel 100 kHz FFT spectrum analyzer |

|

Digital Phosphor Oscilloscope |

DPO |

DPO 70404C |

4 GHz digital oscilloscope |

|

High speed pulse generator |

HSPG |

AVR-E3-B-W3 |

100 V, 1 ns to 5000 ns pulse generator |

|

Arbitrary Function Generator (3 Nos) |

AFG |

AFG1022 |

µHz to MHz, mV to 10 V, dual channel function generator |

|

4 Channel Digital Storage Oscilloscope (2 Nos) |

DSO |

TBS1154 |

150 MHz, 4 channel oscilloscope |

|

Lock-in Amplifier |

MFLI |

MFLI |

500 kHz Lock-In Amplifier |

4. Transmission Line Pulsing

Transmission line pulse setup is used to generate electrical pulses at a very high frequency with high amplitudes. At these frequencies, wavelength of electrical signal reaches the length scales of the testing setup and a proper pulse shaping is difficult. Due to these issues, a conventional SMU cannot be used for this purpose and a specialized strategy is needed. The TLP pulse generator works on the principle of transmission line pulsing technique. The TLP generator can generate pulses in pulse width range of 1ns-1.5 us with a maximum voltage level of 2 kV.

5. Micro Raman, EL/PL Setup with UV and Visible Lasers

Raman spectroscopy works on the principle of inelastic scattering of light by a material. As the light is applied on a material, the following interactions take place: Rayleigh scattering, Stokes scattering and Anti-stokes scattering. Raman setup works on the principle of stokes and anti-stokes scattering, and is used to study chemical and vibrational properties of a material. A laser source with a pre-determined wavelength and power density is used and a charge couple detector is used to capture photons emitted from the material upon interaction with light. The setup has the following two light sources: (1) DPSS, green-colour, 532 nm and (2) UV light, 325 nm. The setup also comprises of electrical part used to study material change with stress application. A cryogenic pump, with an ability of cool down as low as 4K, is integrated with the Raman setup to study device interactions at extremely low temperatures. This study is used to study ambient interactions, photoluminescence, electroluminescence, impact of electrical stress on chemical properties and low temperature vibrational properties of a material.

7. Custom Setup for 2D Material Based Stamping and Device Fabrication inside Glovebox

This custom developed tool provides an inert environment for fabrication of devices using materials sensitive to oxygen and moisture (less than 1ppm of Oxygen and moisture). This enables development of heterostructures using dry transfer setup called stamping stage having high magnification (2000x) microscope and range of nano-manipulators, provides an efficient way to explore fundamental properties and application specific behaviour of various potential materials for electronic applications. The setup also consists of thermal evaporator for metal deposition and wet-bench. Such an assembly of stamping stage and thermal evaporator inside inert atmosphere enables an ultra-clean process for device fabrication.

8. 3K Ultra Low Vibration Close-Loop Cryocooler for Optical and Electrical (DC & RF) Measurements

This tool allows loading devices under ultra-low temperature (3K) condition and enables optical as well as electrical excitations / measurements.

9. L-N2 Semi-automatic Probe Station

This is a L-N2 based semi-automatic probe station. The tool enables DC and RF device characterization, wafer-level reliability, e-test, modelling, or yield analysis for a temperature ranging from 77K to 550K. It is equipped with a probe station control software to automate measurements for 1000s of devices.

10. Deep Level Transient Spectroscopy

This tool allows probing deep level defect / trap states in materials.

11. Thermo Reflectance Spectroscopy

This tool allows probing temperature across a nanoscale device with sub-400nm special resolution and sub-ns time resolution.

12. Wafer Level Semiconductor Device Reliability Characterization Suit

This tool allows to study high field reliability behaviour of semiconductor devices such as HCI, TDDB, NBTI, PBTI and other similar issues in emerging devices.

13. High End Computational Cluster

With over 500 Cores and more than 6TB RAM, this is among the most powerful cluster being used for TCAD simulations and Atomistic computations.

14. Parametric Curve Tracer with sub-50ns pulse I-V measurement capability

The lab has two such systems from Keithley (Keithley 4200 SCS), which consists of 6 medium power SMUs (each), capacitance-voltage measurement unit and two sets of pulse measurement units (PMU). It allows measurement from fA to A. It can also measure pulse I-V characteristics with 50ns pulse width.

15. 1/f Noise Measurement Setup

This enables 1/f Noise measurements in range of devices.

16. 3-Omega setup for thermal conductivity measurements

17. Atomic Force Microscopy (AFM)

AFM with additional modes such as CAFM, KPFM, SThM, STM, SCM, SSRM, IV Spectroscopy, Lthography, Piezoelectric studies, etc which offers flexibility to perform surface studies and material response to electrical studies.

18. Pulse Raman, Wafer Scale Electroluminescence Mapping, Dark Field Microscopy

Setup for pulsed Raman is available for precise material studies. Electroluminescence mapping, dark field microscopy enhances the surface observation capabilities for identification and processing of novel crystals based devices.

19. 67 GHz PNA -X Network Analyzer

PNA -X Network Analyzer by Keysight (N5247) capable of going upto 67 GHz for Semiconductor Characterization.

20. Advanced TLP Setup

Transmission line pulse setup is used to generate electrical pulses at a very high frequency with high amplitudes. At these frequencies, wavelength of electrical signal reaches the length scales of the testing setup and a proper pulse shaping is difficult. Due to these issues, a conventional SMU cannot be used for this purpose and a specialized strategy is needed. The TLP pulse generator works on the principle of transmission line pulsing technique. The TLP generator can generate pulses in pulse width range of 1ns-1.5 us with a maximum voltage level of 2 kV. A better oscilloscope would help in better time domain resolution of the captured waveforms.

21. Wafer Level HBM Tester with Waveform Capture

Our lab specializes in automated commercial testing routines and this wafer level tool aims to test the response of HBM standard at wafer scale to statistically establish the reliability trends. With the waveform capture capability, response of failed devices can be thoroughly analyzed.

22. GaN and SiC transient reliability testing setup

GaN and SiC are some of the most popularly used materials for power applications. Commercial integration of novel power devices calls for thorough understanding of response of all on-chip components to various transients. This setup will help to test and establish the transient reliability of these devices.

23. Transient Interferometric Setup

TIM setup allows a user to map the hotspot movement in the device active area and the pathways thorough which a device would dissipate heat. This is much required while planning thermal layouting of devices.

24. CVD Reactor for Graphene

Graphene is the by-far the most popular 2D material and its electronics-level high quality growth is much needed to be explored.

25. CVD Reactor for TMDs

Chemical vapor deposition setup for large area monolayer TMD growth of high quality. Control on growth step allows for controllable doping and material-level properties.

26. Nanosecond high power pulse IV setup (From Focus Microwave)

Electrical overstressing is a very big reliability concern when planning and designing devices for commercial application grades. Ultrafast time scales and high power SMU setups allows to study degradation and response of devices to electrical overstressing in steps.

Arriving Soon…

Expansion of lab facilities is already underway with new tools and capabilities being added and setup. Extensive reliability exploration and close control on material growth is being achieved to spearhead the novel semiconductor research.

1. 4K cryo-probe station with RF measurement capability (upto 40 GHz)

This tool would allow to go down to ultra-low temperatures and provide a capability to perform RF measurements of devices.

2. Single photon detection setup

3. 10mK Dilution Fridge with 8T Magnet, 24 DC and 10 RF Lines

4. Qubit Control System for upto 2 Qubits

Research Group

PhD Students

- Raising Archana Bairiganjan Mohapatra (M-Tech: IIT Kharagpur)

- Atharv Shrivastava (GATE Rank: 189)

- Deshpande Ajinkya Charudatta (B-Tech: NIT Nagpur, GATE Rank: AIR 377)

- Mayookha S Lekshmi (B-Tech, NIT Calicut, GATE Rank: 2234)

- Megha Yadav (M-Tech: IIT Gandhinagar)

- Bachawar Vinod Kumar (GATE Rank : 924)

- Vettrivelan M (GATE Rank : 485)

- Mayank Yadav (GATE Rank: 955)

- Shravya N Raj (GATE Rank: 1500)

- Shreenidha K K (GATE Rank: 1336)

- Harihar Nath (M-Tech: NIT Delhi)

- Aadil Bashir Dar (NIT Srinagar, IIT Kanpur)

- Harsh Raj (B-Tech + M-Tech: IIT Kanpur, PMRF)

- Mitesh Goyal (B-Tech: NIT Trichy, Associate Director, Samsung)

- Subhajit Majumder (B-Tech: IIST Trivandrum, Senior Engineering Scientist, ISRO)

- Mehak Ashraf Mir (JMI, NIT Srinagar, PMRF)

- Asif Altaf Shah (M-Tech: NIT Srinagar, PMRF)

- Mohammad Ateeb Munshi (M-Tech: NIT Srinagar, PMRF)

- Rasik Rashid (M-Tech: NIT Srinagar, PMRF)

- Anand Rai (B-Tech: NIT Patna, PMRF, GATE Rank: 113)

- Utpreksh Patbhaje (B-Tech: IIIT Jabalpur, PMRF, GATE Rank: 925)

- Rupali Verma (B-Tech: NIT Patna, PMRF)

- Pavithra N (Primary Guide: Prof. Praveen Ramamoorthy)

-

Rajarshi Roy Chaudhuri (M-Tech: IIEST Shibpur, Inspire Fellow, Current Joint PostDoc Fellow with Infineon Technologies and TU Vienna, Austria)

- Monish Murali (2023, B-Tech: PESIT, GATE Rank: 397, TI Fellow, Currently with Texas Instruments)

- Aakanksha Mishra (Joint PhD Students with IIT Delhi, Now with Infineon Technology, Munich, Germany)

- Vipin Joshi (Joint PhD Students with IIT Jodhpur, Now Assistant Professor in BITS Pilani, Goa Campus)

- Sayak Dutta Gupta (2022, M-Tech: IIEST Shibpur, Inspire Fellow, Joined Infineon Technologies, Germany, Currently Assistant Professor in IIT Madras)

- Jeevesh Kumar (2022, B-Tech: NIT Trichy, CSIR-UGC NET Rank: 71, CSIR Fellow, Currently Assistant Professor in IIT Dhanbad)

- Harsha B (2022, B-Tech: GEC Trissur, GATE Rank: 414, Currently with AOS)

- Hemanjaneyulu Kuruva (2021, M-Tech: IISc Bangalore, Visvesvaraya Fellow, Currently with Lam Research)

-

Ansh (2021, B-Tech: NERIST Itanagar, UT Austin, Fulbright Fellow, IMEC, Belgium, Currently with Micron, USA)

- Kranthi N. K. (2021, M-Tech: NIT Calicut, Visvesvaraya Fellow, Currently with Texas Instruments)

- Ankit Soni (2021, B-Tech: NIT Hamirpur, GATE Rank: 864, Visvesvaraya Fellow, Now with Nexperia, UK)

- Rajat Sinha (2021, B-Tech: BIT Mesra, GATE Rank: ~500, Currently with Micron)

- Bhawani Shankar (2020, M-Tech: BITS Pilani, Stanford University, Currently with Power Integrations, USA)

- Adil Meersha (2020, B-Tech: NIT Calicut, GATE Rank: 21, University of Cambridge, Currently with Paragraf (A Graphene Company), UK)

- Abhishek Mishra (2020, M-Tech: IIITM Gwalior, University of Bristol, Currently with A-Star, Singapore)

- Milova Paul (2020, M-Tech: DTU Delhi, Currently with Intel, Portland, USA)

- Sampath B (2020, M-Tech: NIT Nagpur, Currently with Global Foundry, Singapore)

Postdoctoral Fellow

- Mahesh Vaidya (Ph.D. NIT Raipur, Samsung Fellow)

- Vipin Joshi (Ph.D. IITJ, Currently Assistant Professor in BITS Goa)

- Jeevesh Kumar (Ph.D. IISc, Currently Assistant Professor in IIT Dhanbad)

- Harsha B Variar (Ph.D. IISc, Currently with AOS)

- Suruchi Sharma (Ph.D. NIT Delhi, Currently with AOS)

- Satendra Kumar Gautam (Ph.D. IIT Roorkee, Currently with Nexperia, UK)

- Kalyan Jyoti Sarkar (Ph.D. IIT Kharagpur, DST SERB NPDF, Now with TU Dresden)

- Ashita Kumar (AOS Fellow)

- Nikhil K S (Ph.D. IITM, Assistant Professor, NIT Calicut)

- Asha Yadav (Ph.D. IITG, Currently with University of Calgary)

- Jhnanesh Somayaji (Ph.D. NIT Karnataka, Currently with Global Foundry)

- Ajay (Currently with Global Foundry)

- Vinila Bedekar (Ph.D. BARC, Currently with FutureBridge)

Trained and Guided over 100 Masters Students and Project Staff

Teaching

Course title (Click to see Syllabus)

1. Basics of Semiconductor Devices and Technology

2. Microelectronics Lab

3. Physics and Design of Transistors

4. Design of Power Semiconductor Devices

5. Reliability of Nanoscale Circuits and Systems

6. Design of Power Semiconductor Devices

7. Microelectronics Technology For VLSI Engineers

8. VLSI Design Principles for Device Engineers

Professional Recognitions, Awards, and Fellowships

- SwarnaJayanti Fellowship, DST, 2021 – 2026

- VASVIK Award, Year 2021

- IEEE Electron Devices Society Board of Governors (2023 – 2025)

- IEEE Electron Devices Society Distinguished Lecturer

- Editor, IEEE Transactions on Electron Devices (2022 – 2025)

- Editor, IEEE Transactions on Materials for Electron Devices (2025 – 2027)

- Abdul Kalam Technology Innovation National Fellowship, INAE, 2021 – 2026

- National Academy of Sciences, India, (NASI) Young Scientist Platinum Jubilee Award – 2018

- Indian National Academy of Science (INSA) Young Scientist Award, 2018

- Indian National Academy of Engineering (INAE) Innovator Entrepreneur Award 2018 (Special commendation)

- Indian National Academy of Engineering (INAE) Young Engineer Award, 2017

- IEEE EDS Early Career Award – 2015, one of the highest honors given by IEEE Electron Device Society (EDS).

- INAE Young Associate (since 2017)

- Indian Academy of Sciences (IASc), Young Associate, 2018 – 2023

- Department of Electronics & Information Technology (DeitY), Govt. of India, Young Faculty Fellowship for the duration of 2016 – 2020.

- Outstanding Paper Award, 38th EOSESD Symposium, 2017

- Best Paper Award, 30th IEEE VLSI Design Conference, Jan. 2017

- Best Paper Award, 6th IEEE ICEE, Dec 2022

- Editor for Elsevier Microelectronic Reliability (2018 – 2020)

- TR35, 2010, Young Innovator Award. Technology Review’s TR35 list by Massachusetts Institute of Technology recognizes the outstanding innovators under the age of 35 each year. Received on March 8, 2010

- Award for Excellence in Thesis Work, IIT Bombay-2010, received on 6th August, at the 48th convocation of IIT Bombay.

- IIT Bombay – Industrial Impact Award, for pursuing research work that caused maximum industry impact. Received on September 6, 2010 by Dr. N. Mukunda, who is a prominent Indian scientist.

- Best Research paper Award, Intel Asia Academic Forum 2008, Oct 2008, Taipei, Taiwan

- Infineon Fellowship, Duration: November 2008- July 2010

- IEEE Electron Device Society Committees

- Technical Committee for Wideband gap Semiconductors

- Technical Committee for Reliability Physics

- Membership Committee

- Conference Leadership & Technical Program Committee (TPC) IEDM and IRPS are the two most prestigious conferences

-

- General Co-Chair, IEEE EDTM, 2024

- Sponsorship Co-Chair, IEEE EDTM, 2023

- Organizer, 14th RPGR (Recent Progress in Graphene Research), 2023

- General Chair, IEEE ICEE, 2022

- Sub-committee Chair, EOSESD Symposium, USA, 2021

- Technical Program Committee, IEEE EDTM, 2019

- General co-Chair, IEEE ICEE, 2020

- Technical Program Committee Chair, IEEE ICEE, 2018

- General co-Chair and Technical Program Committee Chair, IEEE CONECCT, 2018

- Technical Program Committee, IEEE International Electron Device Meeting (IEDM), 2019

- Technical Program Committee, IEEE International Electron Device Meeting (IEDM), 2018

- Vice-chair, “Device and Process Technology” Track, IEEE VLSI Design Conference, 2014 & 2015

- IEEE International Reliability Physics Symposium (IRPS), USA, 2017 – 2021

- Sub-committee Chair, EOSESD Symposium, 2017

- IEEE ESREF, Europe, 2019

- IEEE ESSDERC, Europe, 2014 – 2016

- Sub-committee Chair, EOSESD Symposium, 2014

- Technical Program Committee, EOSESD Symposium, 2012 – 2021

- General Chair, India ESD Workshop, 2015 – 2020

Science Outreach Through Electronic and Print Media

With IISc Affiliation:

Deccan Herald: https://www.deccanherald.com/india/karnataka/bengaluru/iisc-synopsys-tie-up-to-train-next-gen-semiconductor-workforce-2740179

NDTV: https://www.ndtv.com/education/iisc-software-company-synopsys-collaborate-to-bridge-indias-semiconductor-workforce-gap-4506616

Notopedia: https://www.notopedia.com/board-details/28607/1/IISc-And-Synopsys-Partner-To-Close-Semiconductor-Workforce-Gap-In-India

Techmag: https://www.technologymagazine.org/iisc-partners-with-synopsys-to-train-next-generation-semiconductor-workforce/

IISc Bulletin: https://iisc.ac.in/events/iisc-and-synopsys-collaborate-to-address-the-global-semiconductor-workforce-shortage/

BusinessLine: https://www.thehindubusinessline.com/companies/samsung-iisc-sign-mou-to-set-up-quantum-technology-lab/article67438414.ece

The Economic Times: https://economictimes.indiatimes.com/tech/technology/samsung-semiconductor-india-research-iisc-in-pact-for-research-on-quantum-technologies/articleshow/104554472.cms

The Indian Express: https://indianexpress.com/article/cities/bangalore/samsung-semiconductor-india-research-iisc-quantum-technology-lab-8991203/

Times Now: https://www.timesnownews.com/education/iisc-samsung-semiconductor-india-research-collaborate-to-set-up-a-quantum-technology-lab-article-104570527

EE Times: https://www.eetindia.co.in/samsung-semiconductor-and-iisc-collaborate-on-quantum-research/

Analytics India Magazine: https://analyticsindiamag.com/samsung-and-iisc-partner-to-set-up-a-quantum-technology-lab/

Business World: https://www.businessworld.in/article/Samsung-IISc-Join-Forces-To-Establish-Quantum-Technology-Lab/19-10-2023-495624/

Digital Learning: https://digitallearning.eletsonline.com/2023/10/iisc-and-ssir-ink-mou-to-establish-quantum-technology-lab/

Pune News: https://pune.news/science/quantum-technology-research-gets-a-boost-as-samsung-joins-forces-with-iisc-70666/

IISc Bulletin: https://iisc.ac.in/events/samsung-semiconductor-india-research-and-indian-institute-of-science-collaborate-to-drive-research-on-quantum-technologies/

Financial Express: https://www.financialexpress.com/education-2/ssir-and-indian-institute-of-science-join-hands-to-boost-semiconductor-rampd-in-india/2975087/

Economic Times: https://economictimes.indiatimes.com/tech/technology/samsung-semiconductor-india-research-iisc-join-hands-to-boost-india-semiconductor-rd/articleshow/97726429.cms

ToI: https://timesofindia.indiatimes.com/business/india-business/samsung-semiconductor-india-research-and-indian-institute-of-science-partner-to-boost-semiconductor-rd/articleshow/97728143.cms

Analytics India: https://analyticsindiamag.com/samsung-partners-with-iisc-to-drive-semiconductor-innovation/

The Hindu: https://www.thehindubusinessline.com/business-tech/samsung-semiconductor-india-research-iisc-partner-to-boost-rd-in-semiconductor/article66484614.ece/amp/

Deccan Herald: https://www.deccanherald.com/amp/business/technology/iisc-samsung-wing-join-hands-for-semiconductor-rd-project-1189126.html

Outlook India: https://www.outlookindia.com/business/iisc-to-collaborate-with-samsung-in-advanced-nanoelectronics-device-research-news-260490

PTI News: https://www.ptinews.com/news/business/iisc-to-collaborate-with-samsung-in-advanced-nanoelectronics-device-research/4/510189.html

Economic Times: https://auto.economictimes.indiatimes.com/news/auto-components/iisc-technology-can-address-automotive-chip-shortage/89987058

News 18: https://www.news18.com/news/auto/researchers-at-iisc-collaborating-to-provide-solution-for-chip-shortage-in-auto-industry-4837550.html

Indian Express: https://indianexpress.com/article/cities/bangalore/iisc-bengaluru-research-chip-shortage-7800829/

Bhaskar: https://www.bhaskarlive.in/iisc-technology-can-address-automotive-chip-shortage/

My News 24×7: https://mynews24x7.in/iisc-technology-can-address-automotive-chip-shortage-et-auto/

News Network: https://todaynewsnetwork.in/indian-institute-of-science-technology-could-help-address-automotive-chip-shortage/

Times Bureau: https://thetimesbureau.com/to-solve-chip-shortages-iisc-researchers-have-developed-a-resilient-high-voltage-automotive-technology-platform-202203/

Business Bytes: https://www.buzinessbytes.com/technology/iisc-technology-can-address-automotive-chip-shortage/

Lokmat Times: https://www.lokmattimes.com/technology/iisc-technology-can-address-automotive-chip-shortage/

Gadgets Now: https://www.gadgetsnow.com/tech-news/iisc-technology-can-address-automotive-chip-shortage/amp_articleshow/89991291.cms

Ahmedabad Mirror: https://ahmedabadmirror.com/iisc-technology-can-address-automotive-chip-shortage/81823583.html

India Today: https://www.indiatoday.in/education-today/news/story/iisc-bangalore-s-swarnajayanti-awardee-is-researching-on-materials-to-make-computers-more-efficient-1907180-2022-02-01

DST: https://dst.gov.in/swarnajayanti-awardee-bangalore-working-materials-can-make-computers-more-efficient

Telegraph: https://www.telegraphindia.com/edugraph/news/iisc-bangalore-professor-researches-on-mimicking-functions-that-the-brain-can-perform-rapidly/cid/1850185

Business Insider: https://www.businessinsider.in/science/research/news/iisc-scientist-develops-material-that-can-help-computers-mimic-brain-like-functions/articleshow/89263106.cms

Deccan Herald: https://www.deccanherald.com/science-and-environment/iisc-scientist-brings-out-material-that-can-help-computers-mimic-human-brain-function-1076764.html

Kalinga TV: https://kalingatv.com/technology/iisc-scientist-brings-out-material-that-can-help-computers-mimic-human-brain-function/

Gadgets Now: https://www.gadgetsnow.com/tech-news/iisc-scientist-brings-out-material-that-can-help-computers-mimic-human-brain-function/amp_articleshow/89264611.cms

National Herald: https://www.nationalheraldindia.com/amp/story/science-and-tech/iisc-scientist-brings-out-material-that-can-help-computers-mimic-human-brain-function

Ahmedabad Mirror: https://ahmedabadmirror.com/iisc-scientist-brings-out-material-that-can-help-computers-mimic-human-brain-function/81819733.html

Social News: https://www.socialnews.xyz/2022/01/31/iisc-scientist-brings-out-material-that-can-help-computers-mimic-human-brain-function/

Tripura India: https://www.tripuraindia.in/update/index/iisc-scientist-brings-out-material-that-can-help-computers-mimic-human-brain-function

Block One Daily: https://blockonedaily.com/iisc-scientist-brings-out-material-that-can-help-computers-mimic-human-brain-function/

Mangalore Mirror: https://www.mangaloremirror.com/swarnajayanti-awardee-from-bangalore-working-on-materials-that-can-make-computers-more-efficient/

Indian Express: https://indianexpress.com/article/cities/bangalore/bengaluru-scientists-swarnajayanti-fellowships-7613187/

IISc Press: https://iisc.ac.in/events/35034/

Aljazeera: https://www.aljazeera.co.in/business/three-bengaluru-scientists-awarded-swarnajayanti-fellowships/

New Indian Express: https://www.newindianexpress.com/cities/bengaluru/2021/nov/09/three-bengaluru-scientists-get-swarnajayanti-fellowships-2381168.html

Republic World: https://m.republicworld.com/india-news/education/17-scientists-awarded-swarnajayanti-fellowships-for-innovative-research-ideas.html

Business Bytes: https://www.buzinessbytes.com/news/national-news/swarnajayanti-fellowship-awarded-to-scientists-from-bangalore/

Ministry of Science & Technology (English Release): https://pib.gov.in/PressReleasePage.aspx?PRID=1705691

Ministry of Science & Technology (Hindi Release): https://pib.gov.in/PressReleasePage.aspx?PRID=1705750

DST: https://dst.gov.in/new-technology-high-electron-mobility-transistor-will-make-india-self-reliant-power-transistor

Bangalore Mirror: https://bangaloremirror.indiatimes.com/bangalore/cover-story/e-ncredible-india/articleshow/81575854.cms

Kashmir News: https://kashmirnewsbureau.com/scientists-from-bangalore-develop-highly-reliable-hemt/

Swarajya Magazine: https://swarajyamag.com/insta/indian-scientists-develop-indigenous-normally-off-high-electron-mobility-transistor-for-power-electronics

News20: https://news20-20.com/new-technology-for-hemt-developed/

Adda247: https://www.adda247.com/upsc-exam/daily-gist-of-the-hindu-pib-indian-express-and-other-newspapers-18-march-2021/

Rajya Sabha TV: https://www.youtube.com/watch?v=ASJ2H-NV7hw

Research Matters: https://researchmatters.in/news/iisc-develops-india%E2%80%99s-first-e-mode-gallium-nitride-power-transistor

Times of India: https://timesofindia.indiatimes.com/home/science/iisc-faculty-change-game-with-indias-first-e-mode-gallium-nitrade-power-transistor/articleshow/69661844.cms

Electronic for You: https://academia.electronicsforu.com/iisc-researchers-develop-indias-first-e-mode-gallium-nitride-power-transistor

Northbound: http://www.northbound.co.in/engineering-phd/

Research Matters: https://researchmatters.in/news/iisc-research-pushes-reliability-and-operating-limits-ultra-dense-finfet-system-chips

EE Herald: http://www.eeherald.com/section/news/owns20171225001-india-ee-edu.html

Research Matters: https://researchmatters.in/article/inae-announces-young-engineer-awards-2017

India DST: https://indiadst.wordpress.com/2017/01/20/iisc-researchers-develop-new-graphene-based-transistor-technology/

Scientifist: http://scientifist.com/iisc-researchers-graphene-electronics/

Indian Express: http://indianexpress.com/article/technology/science/breaking-the-graphene-barrier-4465396/

Bangalore Mirror: http://bangaloremirror.indiatimes.com/bangalore/others/iisc-can-make-your-wifi-1000-times-faster/articleshow/56091767.cms

IISc Press: https://researchmatters.in/article/iisc-scientists-new-discovery-yields-giant-leap-graphene-transistor-performance

The Better India: http://www.thebetterindia.com/79060/iisc-working-making-wifi-1000-times-faster/

UC News: http://www.ucnews.in/news/702-513932134192309/a-team-of-researchers-from-iisc-bangalore-could-make-our-wifi-1000-times-faster.html

Yahoo: https://in.news.yahoo.com/team-researchers-iisc-bangalore-could-095934372.html

Indian 364: http://www.indian364.com/technology/26961/Breaking-the-graphene-barrier

Research Matters: https://researchmatters.in/article/iisc-scientists-new-discovery-yields-giant-leap-graphene-transistor-performance

Rajya Sabha TV: https://youtu.be/k9u2Ji9Vlbk

Bangalore Mirror: http://www.bangaloremirror.com/bangalore/others/New-transistor-design-is-a-breakthrough/articleshow/49897633.cms

Indian Express: http://indianexpress.com/article/technology/technology-others/from-the-lab-a-new-device-for-more-efficient-phones-computers/

IISc Press: http://iisc.researchmedia.center/article/iisc-researcher%E2%80%99s-new-transistor-design-%E2%80%93-breakthrough-chip-technology

Indian Express: http://www.newindianexpress.com/cities/bengaluru/IISc-Prof-Wins-Major-Global-Award/2015/10/29/article3102225.ece

Deccan Herald: http://www.deccanherald.com/content/515146/bengaluru-scientist-wins-coveted-ieee.html

Hindu: http://www.thehindu.com/news/cities/bangalore/honour-for-iisc-professor/article7816056.ece

Global Indians: http://www.globalindian.indiaincorporated.com/iisc-prof-wins-major-global-award/

IEEE: http://eds.ieee.org/early-career-award.html

IISc Press:: http://iisc.researchmedia.center/article/iisc-professor-wins-major-international-award

Deccan Herald: http://www.deccanherald.com/content/509822/iisc-faculty-devises-technology-shrink.html

News Central: http://newscentral.exsees.com/item/8563b69c9b5b9519487c36e18dcedb90-f39db1effc9ea34e1d52a76b94b3ea02

Gas & Electricity: http://gaselectricity.in/iisc-faculty-devises-technology-to-shrink-power-electronic-systems

Daily Hunt: http://m.dailyhunt.in/news/india/english/deccan-herald-epaper-deccan/iisc-faculty-devises-technology-to-shrink-power-electronic-systems-newsid-45850179

Nyooz: https://www.nyoooz.com/news/bengaluru/245362/iisc-prof-wins-major-global-award/

GK Today: https://www.gktoday.in/quiz-questions/who-became-the-first-indian-to-bag-ieee-electron-devices-society-early-career-award/

Before joining IISc:

Technology Review: http://www2.technologyreview.com/tr35/profile.aspx?TRID=860

DNA: http://www.dnaindia.com/india/report-iit-b-makes-it-to-mit-s-top-innovators-list-1361475

Deccan Herald: http://www.deccanherald.com/content/58465/beyond-classroom.html

Indian Express: http://www.indianexpress.com/news/towards-smaller-better-gadgets/587650/0

NDTV: http://www.ndtv.com/news/sci-tech/iit_infineon_achieve_breakthrough_for_system-on-chip.php

EE Herald: http://www.eeherald.com/section/news/nw10000592.html

EE Times: http://www.eetimes.com/author.asp?section_id=36&doc_id=1284049

EE Times: http://www.eetimes.com/electronics-news/4083184/Infineon-Indian-researchers-claim-ESD-advance

Rediff: http://business.rediff.com/report/2009/apr/22/iit-achieves-breakthrough.htm

Science Outreach Through Invited Talks

(Other than peer reviewed presentations)

1. “A Roadmap for Disruptive Applications & Heterogeneous Integration using 2-Dimensional Materials: State-of-the-Art and Technological Challenges”

-

- IEEE Bangalore Semicon Industry Forum, Intel, Eco Space office, Bangalore (12th April, 2025)

- ICFM 2024, IIT KGP (9-11th January, 2024)

- IEEE DL Talk, IIT Bombay (January 12, 2024)

- National Physicists’ Conclave 2024 (7th February, 2024)

- R&S Tech Symposium India 2024 (April 23rd, 25th, 2024)

- IEEE Talk at IIT Guwahati (24th October, 2024)

- Invited Talk, ASML, Veldhoven, Netherlands

- Invited Talk, IMEC, Leuven, Belgium

- Invited Talk, Recent Progress in Graphene and 2D materials Research (RPGR, 2023)

- 2023 NANOscientific Symposium Asia, Keynote Talk

- 2023 International ESD Workshop & IEEE IRPS, Keynote Talk

- IEEE Distinguished Lecture, IEEE EDS Malaysia Chapter

- IEEE Distinguished Lecture, IEEE EDS IIT Roorkee Chapter

- 2023, Heights Researcher’s Fest, University of Kerala (Trivandrum)

- Invited Talk, IISER Thiruvananthapuram

2. “The Future of World Electronics and the Possible Role India Can Play”

-

- Distinguished Lecture, IEEE Sensors Council, NIT Jodhpur

- Shrimati Indira Gandhi College, Tiruchirappalli

- Bangalore Nano, March 2022

- IIT Indore, March 2022

- IIT Patna, Dec 2021

- Distinguished Lecture, IEEE SJC EDS Chapter, Oct. 2021

- IIIT Kancheepuram, Oct. 2021

- TBI CPDMED CEFC Design Manufacturing and Entrepreneurship Series, Aug. 2021

- Distinguished Lecture, IEEE CAS Chapter, Feb. 2021

- Distinguished Lecture, NIT Jalandhar, Sep. 2020

- Distinguished Lecture, IEEE Bangalore Section, June 2020

- IEEE Mini-Colloquium, Delhi University, Sep. 6th 2019

- School of Physics at the IISER, Thiruvananthapuram, August 24th 2019

- Workshop on Microelectronics and Information Security, SSPL, Ministry of Defense, Oct. 2018

- 41st Annual event of KSCST (August 12th 2018)

- Innovation Bazar, Western Digital (July 6th 2018)

- IEEE Talk, Madras Chapter (Dec 26th 2017)

- SSPL, DRDO (Oct. 2017)

- IEEE Region – 10 Golden Jubilee Event, August 5th, 2017 (Key Note Talk)

- 51st Computer Society of India Conference (Memorial Talk, Jan. 24th 2016)

- IEEE Golden Jubilee Congress (August 2016)

- IISc EECS Symposium (Feb 2016)

3. “Gallium Nitride Electronics: Design and Reliability / e-mode HEMTs / Physics of Dynamic Ron”

-

- Invited Talk, NXP, Nijmegen, Netherlands, Oct. 2023

- Invited Talk, Nexperia, Munic, Germany, Oct. 2023

- IEEE Talk, UCLA, USA, April, 2023

- Invited Talk, XXII International Workshop on Physics of Semiconductor Devices (IWPSD), 2023

- Indo-French Workshop, IIT Madras, Feb, 2023

- GaN Marathon 2022, Venice, Italy, June, 2022

- IWPSD – Invited Talk, Dec, 2021

- 5th IEEE ICEE – Invited Talk, Dec, 2020

- University of Padova, Padova, Italy, July, 2018)

- Infineon Technology, Villach, Austria, July, 2018)

- Online webinar organized by ESD Association USA, telecasted globally on 29th Nov. 2017.

- Invited Talk, IWPSD, Dec. 2017

- Invited Talk, ITC-India, July 2017

- Invited Talk, ICYRAM-2016, Dec. 14th 2016

- Invited Talk, Texas Instruments, Dallas, April, 2017

- Invited Talk, Semiconductor Complex Limited (SCL), Department of Space, May 2017

- IEEE Conference, July 11th, 2017

- International Conference on Emerging Electronics, Dec. 5th 2014

4. “Atomic Orbital Overlap Engineering for 3D-2D Contacts & Record High-Performance 2D Transistors”

-

- Distinguished Lecture, IIIT Kanchipuram, Feb 22nd, 2023

- IIT Madras, Feb 21st, 2023

- NIT Jaipur, Feb 13th, 2023

- ASET Colloquium Talk, TIFR, Mumbai, July 2022

- DST Workshop, INST Mohali, August 2022

- Distinguished Lecture, IIT BHU, August 2022

- LIT Talk, IIT Bombay, July 2022

- Invited talk at IWPSD – Dec 2019

- IEEE ICEE, IIT Delhi, Nov. 2020

- University of Budweiser, Munich, Germany, July 4th 2018

- ISIF, Dec, 2017

- IEEE International Conference on Emerging Electronics, Dec. 27th 2016

- IIT Delhi, Jan 9th 2017

- IIT Kanpur, Jan 10th 2017

5. “Why Ph.D.? – Breaking the myths and misconceptions about Ph.D. and a guide to becoming a successful researcher”

-

- India Science Festival, IISER Pune (20th and 21st January, 2024)

- IEEE Talk at IIT Guwahati (24th October, 2024)

- Public Lecture, IIT Roorkee

- 2023, Heights Researcher’s Fest, University of Kerala (Trivandrum)

- Public Lecture, IISER Thiruvananthapuram

- Public Lecture, IIIT Kanchipuram

- Public Lecture, IIT Madras

- Public Lecture, NIT Jaipur

6. New Insights into ESD and HV Phenomena & ESD/HV Design Approaches in Silicon Technology Nodes

-

- X-FAB, Erfurt, Germany

- NXP, Nijmegen, Netherlands

- Nexperia, Nijmegen, Netherlands

- Infineon, Munich, Germany

- Intel, Munich, Germany

- Analog Device, USA

7. “On-Chip ESD Devices and Circuits: Essentials and Research Opportunities”

-

- 3rd India ESD Workshop, Feb 25th, 2019

- 2nd India ESD Workshop, March 17th, 2017

- 1st India ESD Workshop, Feb 26th, 2016

- IIT Gandhinagar, Dec. 31st 2015

- Semiconductor Complex Limited (SCL), Department of Space, July 1st 2015

- EE Department, IIT Madras, July 2014

- Texas Instruments Bangalore, India, April 2014

- CRL Bangalore, Feb. 2014

- Fifth Electrical Sciences Symposium, IISc Bangalore, Feb. 2014

8. “ESD Design Essentials”, Bangalore, 8th and 9th Jan. 2015

-

- ESD Device Physics

- On-Chip ESD (Circuit) Design

- CDM Phenomena and Protection Design

- Latch-up

9. “How Experimental and Computational Probes Enabled Development of (India’s First) GaN Based Power Transistor and Diode Technologies”

-

- The Third Indian Materials Conclave and the 32nd Annual General Meeting of MRSI, Dec 2021

- IWPSD, IIT Delhi, Dec 2021

- IEEE ICEE, IIT Delhi, Nov. 2020

10. “A Vision for India to Lead in Semiconductor R&D and Manufacturing (What, Why & How?)”

-

- Colosseum 2025, Don Bosco Institute of Technology (DBIT), Mumbai (6th March, 2025)

- IIST and IIT Dhanbad, On the occasion of laying the foundation for three semiconductor facilities by the Hon’ble Prime Minister (12th March, 2024)

- Tektronix Semicon Skill India Program (3rd May, 2024)

- GTX Technology Game Changers Series (9th May 2024)

- TalentSprint Webinar (4th July, 2024)

- Invited Talk by GTU, Gujarat (9th September, 2024)

- Semiconductor Ecosystem: Awareness and Opportunities for Northeast India (25th October, 2024)

- Bangalore Nano, March 2022

- World Congress on Micro Nano Manufacturing, IIT Bombay, Sep. 2021

- VAIBHAV Summit, Oct. 2020

11. “ESD Device Physics of Advance and Beyond CMOS Devices”

-

- Intel Corp., Munich, Germany (July 27th 2018)

- Infineon Technology, Munich, Germany (July 28th 2018)

- Intel Corp., Portland, USA (Sep 19th 2018)

- NXP, Nijmegen, Netherlands (June 29th, 2018)

12. “Performance & Reliability Co-Design Approach for High Voltage LDMOS Devices”

-

- Infineon Technology, Munich and Kuching, Oct. 2020

- NXP, Nijmegen, Netherlands (June 29th, 2018)

- Semiconductor Complex Limited (SCL), Department of Space, July 2nd 2015

- ANURAG, DRDO, Feb 2017

- LRDE, DRDO, Feb 2017

13. Panel Discussion: Innovator Stories: From Idea to Impact, World Intellectual Property (IP) Day 2025 celebration, IISc Bangalore, (25th April, 2025)

14. “Next Generation Semiconductor Technologies for Advanced Systems”, R&S Tech Symposium India 2025, Hotel Radisson Blu, Bangalore (24th April, 2025)

15. Predictive TCAD-Based ESD Design without Foundry Data, 5th India ESD Workshop (23rd August, 2024)

16. Easing the Technological & Reliability Challenges of e-Mode AlGaN/GaN HEMTs by p-type AlTiO Based Gate Stack and Passivation Engineering, Monthly 2XP Distinguished Lecturer Series by NXP Semiconductors (3rd September, 2024)

17. Panel Discussion: The ART of System Design, Western Digital’s Times Techie Webinar (3rd September, 2024)

18. From Sand to Silicon: The Journey of Semiconductor Industry in Technology Development, Invited Talk by GTU, Gujarat (9th September, 2024)

19. How Wide Bandgap Semiconductors Like GaN Can Transform Power Electronics Industry?”, Keynote Talk, Cyient Power Electronics Conference, Oct. 2021

20. “THz Electronics Opportunities and R&D Challenges”, Invited talk in the International Workshop on THz Technology, IIT Delhi, Sep 21st 2019

21. “Towards the end of Moore’s Law: Options and Challenges Beyond Advanced FinFET Technologies to Sustain CMOS ULSI”, Tutorial talk at IWPSD – Dec 2019

22. “ESD Reliability and Physics of Carbon Electronics”, International ESD Workshop, USA, 1st April, 2019

23. “On Chip ESD Design: Why EDA Based Approach is Becoming Important?”, Keynote talk at Cadence India Design Center, Dec 11th 2015

24. “ESD Robust LDMOS Design Essentials” Online webinar organized by ESD Association USA, telecasted globally in Nov. 2014.

25. “IC and System Design for Electrostatic Discharge Protection”, IEEE INDICON, Dec. 2013

26. “Drain extended MOS device design and reliability challenges” IWPSD Dec. 2013

27. “A Review on the ESD Robustness of Drain Extended MOS Devices” International ESD workshop, May 20, 2013, Warrenton, VA, USA

28. “3D TCAD Based approach for ESD failure analysis”, Infineon Technologies, AG, Munich (Germany), June 2010.

29. “Reliability aware I/O design for sub 45nm node CMOS technology” IWPSD-2009, 18th Dec, 2009.

30. “Benchmarking the device performance at sub 22 nm node technologies using an SoC framework”, IWSG-2009, 3rd Dec 2009.

31. “3D filament behavior of various HV DeMOS devices under ESD condition” University of California (SB), USA, 4th Sep, 2009.

32. “Filament behavior of various DeMOS devices”, Technical University of Vienna, Austria, 8th Oct 2008.

33. “ESD optimization of DeMOS devices”, Infineon Technologies, AG, Munich (Germany), 6th Oct 2008.

34. “Mixed signal and hot carrier performance of various DeMOS devices” Infineon Technologies, AG, Munich (Germany), 3rd May 2008.

Patents

Granted Patents (#1 – #31 are granted in US, #1 – #20 granted in two or more than two countries, #32 – #39 granted in India):

- Rajesh Thakkar, Mayank Shrivastava, M. Shojaei, D. K. Sharma, V. Ramgopal Rao, M. B. Patil, “Operational Amplifier Having Improved Slew Rate ” United States Patent (03-01-2012) 8,089,314 (Also filed/granted in other countries, India: 542/MUM/2010, European Patent: EP2543141; Chinese Patent: CN102474230; and PCT: WO2011107824)

- Mayank Shrivastava, M. Shojaei, D. K. Sharma, V. Ramgopal Rao, “Nonvolatile floating gate analog memory cell”, United States Patent (07-05-2013) 8,436,413 (Also filed/granted in other countries, Indian Patent No 258773; and PCT: WO2010046922.)

- Mayank Shrivastava, Harald Gossner, V. Ramgopal Rao, M. Shojaei,” Semiconductor devices with trench isolations”, United States Patent (17-01-2012) 8,097,930 (Also granted in Germany, Patent No: DE102009034405)

- Mayank Shrivastava, Harald Gossner, V. Ramgopal Rao, M. Shojaei, “Field-effect device and manufacturing method thereof”, United States Patent (15-01-2013) 8,354,710 (Also granted in Germany, Patent No: DE102009030086)

- Mayank Shrivastava, Harald Gossner, Maryam Shojaei Baghini, Ramgopal Rao, Christian Russ, “Device and method for coupling first and second device portions”, United States Patent (04-06-2013) 8,455,947 (Also granted in Germany, Patent No: DE102010000355)

- Mayank Shrivastava, Christian Russ, Harald Gossner, V. Ramgopal Rao, “Drain extended field effect transistors and methods of formation thereof”, United States Patent (17-09-2013) 8,536,648 (Also granted in Germany, Patent No: DE102012100767)

- Mayank Shrivastava and Harald Gossner, “Drain extended MOS device for Bulk FinFET technology”, United States Patent (14-01-2014) 8,629,420 (Also granted in Germany, Patent No: DE102013106152; Taiwan, Patent No: TW201411844 and in China, Patent No: CN103531633)

- Mayank Shrivastava, Harald Gossner, V. Ramgopal Rao, M. Shojaei, “Semiconductor devices and methods for manufacturing a semiconductor device”, United States Patent (04-02-2014) 8,643,090 (Also granted in Germany, Patent No: DE102010016000)

- Mayank Shrivastava, Christian Russ, Harald Gossner, “Low voltage ESD clamping using high voltage devices”, United States Patent (18-02-2014) 8,654,491 (Also granted in Germany, Patent No: DE102013103076; and in China, Patent No: CN107424988)

- Mayank Shrivastava, Maryam Shojaei Baghini, Christian Russ, Harald Gossner, Ramgopal Rao, “High voltage semiconductor devices”, United States Patent (04-03-2014) 8,664,720 (Also granted in Germany, Patent No: DE102011050958)

- Mayank Shrivastava, Christian Russ, Harald Gossner, “Selective current pumping to enhance low-voltage ESD clamping using high voltage devices”, United States Patent (25-03-2014) 8,681,461 (Also granted in Germany, Patent No: DE102013103076 and in China, Patent No: CN103367357)

- Mayank Shrivastava and Harald Gossner, “Silicon controlled rectifier (SCR) device for bulk FinFET technology”, United States Patent (22-07-2014) 8,785,968 (Also granted in Taiwan, Patent No: TW201423957)

- Mayank Shrivastava, Christian Russ and Harald Gossner, “Tunable Fin-SCR for Robust ESD Protection”, United States Patent (24-02-2015) 8,963,201.

- Mayank Shrivastava, Harald Gossner, V. Ramgopal Rao, M. Shojaei, “Field-Effect Device and Manufacturing Method Thereof”, United States Patent (19-05-2015) 9,035,375 (Also granted in Germany, Patent No: DE102009030086)

- Mayank Shrivastava, Christian Russ, Harald Gossner, V. Ramgopal Rao, “Drain Extended Field Effect Transistors and Methods of Formation Thereof”, United States Patent (21-07-2015) 9,087,892 (Also granted in Germany, Patent No: DE102012100767).

- Mayank Shrivastava and Christian Russ, “Semiconductor devices and arrangements for electrostatic (ESD) protection”, United States Patent (31-05-2016) 9,356,013.

- Mayank Shrivastava, Maryam Shojaei Baghini, Harald Gossner, Ramgopal Rao, “Methods for manufacturing a semiconductor device”, United States Patent (14-06-2016) 9,368,573 (Also granted in Germany, Patent No: DE102010016000)

- Mayank Shrivastava, Harald Gossner, V. Ramgopal Rao, M. Shojaei, “Field-effect device and manufacturing method thereof”, United States Patent (26-07-2016) 9,401,352 (Also granted in Germany, Patent No: DE102009030086)

- Mayank Shrivastava, Maryam Shojaei Baghini, Christian Russ, Harald Gossner, Ramgopal Rao, “High voltage semiconductor devices”, United States Patent (27-09-2016) 9,455,275. (Also granted in Germany, Patent No: DE102011050958).

- Mayank Shrivastava, Christian Russ, Harald Gossner, V. Ramgopal Rao, “Drain extended field effect transistors and methods of formation thereof”, United States Patent (09-05-2017) 9,647,069. (Also granted in Germany, Patent No: DE102012100767)

- Mayank Shrivastava, Christian Russ and Harald Gossner, “Tunable FIN-SCR for Robust ESD Protection”, United States Patent (28-03-2017) 9,608,098.

- Mayank Shrivastava and Christian Russ, “Semiconductor Devices And Arrangements Including Dummy Gates For Electrostatic Discharge Protection”, United States Patent No: (14-03-2017) 9,595,516.

- Mayank Shrivastava, Milova Paul, Christian Russ and Harald Gossner, “Non-planar Electrostatic Discharge (ESD) Protection Devices With Nano Heat Sinks”, US Patent No (11-06-2019): 10,319,662 (Indian Patent, Application No 201741003773, Filed on 1st Feb. 2017)

- Mayank Shrivastava, Milova Paul, Christian Russ and Harald Gossner, “Low Trigger and Holding Voltage Silicon Controlled Rectifier (SCR) For Non-Planar Technologies”, US Patent No (19-02-2019): 10,211,200 (Indian Patent, Application No 201741003772, Filed on 1st Feb. 2017)

- Mayank Shrivastava, Milova Paul and Harald Gossner, “Electrostatic Discharge (ESD) Protection Devices For ESD Robustness, Latch-Up and Hot Carrier Immunity”, US Patent No (19-11-2019): 10,483,258 (Indian Patent No. 376841)

- Milova Paul, Mayank Shrivastava, Sampath Kumar, Christian Russ and Harald Gossner, “Dual Fin Silicon Controlled Rectifier (SCR) Electrostatic Discharge (ESD) Protection Device”, US Patent No (21-04-2020): 10,629,586 (Indian Patent, Application No 201741003771, Filed on 1st Feb. 2017)

- Mayank Shrivastava, Recess Gate Superjunction High-electron-mobility transistor (HEMT)”, US Patent No (02-02-2020): 10,553,712 (Indian Patent No: 522306, Granted on 08th March 2024.)

- Mayank Shrivastava, Milova Paul and Harald Gossner, “FinFET SCR With SCR Implant Under Anode And Cathode Junctions”, US Patent No (04-02-2020): 10,535,762, (Indian Patent, Application No 201741006746, Filed on 25th Feb. 2017)

- Mayank Shrivastava, Sayak Dutta Gupta, Ankit Soni, Srinivasan Raghavan and Navakanta Bhat, “Enhancement Mode High Electron Mobility Transistor (HEMT)”, US Patent No (17-11-2020): 10,840,348 (Indian Patent Application 201741030570, August 2017)

- Rohit Soman, Ankit Soni, Mayank Shrivastava, S. Raghavan and Navakanta Bhat “High Electron Mobility Transistor (HEMT) with Resurf Junction”, US Patent Application No: US20200227543 A1 (Indian Patent No: 310947)

- Mayank Shrivastava and Vipin Joshi, “Doping and Trap Profile Engineering in GaN Buffer To Maximize AlGaN/GaN HEMT Epi Stack Breakdown Voltage”, US Patent No (08-06-2021):11,031,493 (Indian Patent Application 201841020899, Filled on June 5th 2019)

- Ankit Soni and Mayank Shrivastava, “Novel Drain Connected Field Plate HEMT Designs having Improved Performance”, Indian Patent No: 503229, Grant Date: 25th January 2024

- Ankit Soni and Mayank Shrivastava, “High Electron Mobility Transistor with improved performance and linearity”, Indian Patent No: 510450, Grant Date: 13th February 2024

- Ansh, Hemanjaneyulu Kuruva and Mayank Shrivastava, “Methods of Manufacturing 2-Dimentional Semiconductor Transistors”, Indian Patent No. 482722, Grant Date: 14th Dec. 2023

- N. S. Kranthi, K. Hemanjaneyulu, and Mayank Shrivastava, “A Field Effect Transistor (FET) with Improved Failure Threshold”, Indian Patent No. 441063, Grant Date: 28th July 2023

- Mayank Shrivastava, “Drain extended Tunnel FET”, US Patent Pending, Application No: US2021119044 (A1), Filed on: 23-Feb-17 (Indian Patent No: 470520, Filed on Feb 26th 2016, Grant Date: 20/11/2023

- Mayank Shrivastava and Kuruva Hemanjaneyulu “Fin enabled area scaled tunnel field Effect transistor”, Patent No: 364758, Grant Date: 16/04/2021.

- Mayank Shrivastava, “Drain extended Tunnel FET”, Indian Patent No: 470520, Grant Date: 20th Nov. 2023

- Rasik Rashid and Mayank Shrivastava, “High Electron Mobility Transistor Device”, Indian Patent (Application No: 202241038091) Grant No: 511048, Grant Date: 15th Feb 2024.

- Jatin and Mayank Shrivastava, “Metal Oxide Semiconductor Device Architecture with Uniform Finger Turn On And Method Thereof”, Indian Patent (Application No: 202341026588), Grant No: 509703, Grant Date: 12th Feb. 2024

- Mayank Shrivastava, “A Flexible, Adaptive Neuromorphic Synaptic Chip” Indian Patent No: 512480, Grant Date: 20th February 2024

- Adil Meersha, Mamta Khaneja and Mayank Shrivastava, A Method of Depositing Gate Dielectric on a 2D Material, Indian Patent Number: 517242, Grant Date: 8th Dec. 2024

- Adil Meersha, Mohan Lal and Mayank Shrivastava, Multilayer Graphene Contact for Monolayer Graphene Channel, Indian Patent Number: 560478, Grant Date: 17th May 2024

- Adil Meersha, Jaswant Singh Rawat and Mayank Shrivastava, Method to Selectively Etch h-BN, Indian Patent Number: 543182, Grant Date: 8th Dec. 2024

- Mayank Shrivastava and Rasik Rashid Malik, “Method to Tune Gate Work Function in p-GaN Gate e-mode HEMTs”, Indian Patent (Application No. 202341059980) Grant No: 563081, Grant Date: 21st March 2025.

- Mayank Shrivastava and Anand Kumar Rai, “Doping and Activation Scheme for 2D Semiconductors”, (Application No. 202341059982), Grant No: 562843, Grant Date: 19th March 2025.

- Jatin and Mayank Shrivastava, “Nanosheet Drain Extended MOSFET”, Indian Patent (Application No: 202341007382) Grant No: 549891, Grant Date: 9th Sep. 2024.

- Monishmurali M and Mayank Shrivastava, “Fin-Based SCR Architectures Having Distributed Current Configuration and Enhanced ESD Protection”, Indian Patent (Application No: 202041011502) Grant No: 532990, Grant Date: 15th April 2024.

- Monishmurali M and Mayank Shrivastava, “Low Capacitance FinFET SCR”, Indian Patent No. 566166, Grant Date: 14th May 2025

- Mayank Shrivastava and Rasik Rashid Malik, “A Method for Multiple Passivation Approach in p-GaN Gate e-Mode HEMTs”, Indian Patent (Application No. 202341059983), Patent No: 570711, Grant Date: 16 Sept 2025 (PCT-IN23-2048, filed on 06 Nov 2024).

- Utpreksh Patbhaje and Mayank Shrivastava, “Two-Dimensional (2D) Transition Metal Dichalcogenide Based Analog Memory Device”, Indian Patent (Application No. 202341059978), Patent No. 569113 Granted on 25 July 2025.

Patent Pending:

- Mitesh Goyal, Mukesh Chaturvedi, Mayank Shrivastava, “Gate and Substrate triggered ESD protection silicon-controlled rectifier local clamps for area efficient high speed SERDES.”, Indian Patent Pending.

- Mitesh Goyal, Mukesh Chaturvedi, Mayank Shrivastava, “Area efficient, tunable trigger ESD protection silicon-controlled rectifier local clamps for high speed SERDES.”, Indian Patent Pending.

- Mitesh Goyal, Mukesh Chaturvedi, Mayank Shrivastava, “Low capacitance, area efficient, tunable trigger ESD protection silicon-controlled rectifier with embedded NMOS local clamps for high speed SERDES.”, Indian Patent Pending.

- Mayank Shrivastava and Mohammad Ateeb Munshi, “Gallium Nitride High Electron Mobility Transistor and Method oof Fabricating Semiconductor Device”, Indian Patent Application No: 202541048842, Filing Date: 20th May 2025.

- Rasik Rashid Malik and Mayank Shrivastava, “Gate Metallization Design For E-Mode GaN HEMTs”, Indian Patent Application No: 202441032159, Filing Date: 23rd April 2024.

- Mehak Ashraf Mir and Mayank Shrivastava, “A Surface Passivation for a High Electron Mobility Transistor”, Indian Patent Application No: 202441029855, Filing Date: 12th April 2024.

- Mayank Shrivastava and Mohammad Ateeb Munshi, “Radio Frequency High Electron Mobility Transistors”, Indian Patent Application No: 202541003074, Filing Date: 14th January 2025.

- Mayank Shrivastava and Mayank Yadav, “A Semiconductor Device and Method For Tuning Holding Voltages in Silicon Controlled Rectifier”, Indian Patent Application No: 202541018106, Filing Date: 28th Feb 2025.

- Mitesh Goyal, Mukesh Chaturvedi, Mahesh Vaidya and Mayank Shrivastava, “ESD Protection Circuit With Lower Trigger Voltage and Reduced I/O Capacitance”, Indian Patent Application No: 202441104639, Filing Date: 30th December, 2024

- Mitesh Goyal, Mukesh Chaturvedi, Mahesh Vaidya and Mayank Shrivastava, “Dual Gated, Low Capacitance and Low leakage Dual STI bounded Silicon Controlled Rectifier for STI bounded bulk planar technology”, Patent Pending

- Mayank Shrivastava and Rasik Rashid Malik, “Method of Making High Robustness E-mode High Electron Mobility Transistor”, Application No. 202341059981, filed on 06-Sep-2023

- Mayank Shrivastava and Rasik Rashid Malik, “Method for High Threshold Voltage and High Breakdown Gate Stack in p-GaN Gate e-mode HEMTs”, Application No. 202341059979, filed on 06-Sep-2023

- Jeevesh Kuma, Aadil Bashir Dar and Mayank Shrivastava, “Heat Spreader for System on Chip Device”, Application No. 202341060385, filed on 08-Sep-2023

- Adil Meersha, Prashant Kumar and Mayank Shrivastava, Graphene Transistor with Defected Graphene Layer, Indian Patent Application: 20111057163, Dec. 8th, 2021.

List of Publications

Overall, 275 publications. ~250 publications in IEEE journals (or better) and peer reviewed IEEE conferences of high repute. 63 publications in the IEEE International Electron Devices Meeting (IEDM) & the IEEE International Reliability Physics Symposium (IRPS), which are the two most prestigious conferences for Electron Devices.

Books, Book chapters and Technical Briefs

- Chapter titled “Towards Drain extended FinFETs for SoC applications” in book “Toward Quantum FinFET”, edited by Weihua Han and Zhiming M. Wang, Springer, Dec. 2013, ISBN 978-3-319-02021-1.

- Mayank Shrivastava and V. Ramgopal Rao, “Tunnel Field Effect Transistors”, Present, Past and Future, Technical Brief appeared in the IEEE EDS Newsletters, July 2016 (Cover page article).

Peer Reviewed International Journals

- Mohammad Munshi Ateeb, Mehak Mir Ashraf and Mayank Shrivastava, “Distinct Breakdown Mechanisms Under DC and Pulsed Conditions in AlGaN/GaN HEMTs with Floating Substrate Termination”, to appear in IEEE Transactions on Electron Devices

- Mehak Mir Ashraf, Vipin Joshi, Mohammad Ateeb Munshi, Anup Vitthal Thakare, Rajarshi Roy Chaudhuri and Mayank Shrivastava, “Improving Threshold Voltage and its Stability in p-GaN Gated HEMTs by Mechanical Stress Engineering”, to appear in IEEE Transactions on Electron Devices

- Rasik Rashid Malik, Rajarshi Roy Chaudhuri, Vipin Joshi, and Mayank Shrivastava, “Physical Insights into Turn-ON Mechanisms in p-GaN Gate AlGaN/GaN HEMTs – Part I”, to appear in IEEE Transactions on Electron Devices.

- Rasik Rashid Malik, Vipin Joshi, Saniya Syed Wani, Simran R Karthik, Rajarshi Roy Chaudhuri, Avinas N Shaji, Zubear Khan, and Mayank Shrivastava, “Unique Surface Passivation Stoichiometry Dependence of Dynamic ON Resistance and Its Suppression in p-GaN Gate AlGaN/GaN HEMTs,” to appear in IEEE Transactions on Electron Devices.

- Aadil Bashir Dar, Adil Meersha, Amogh K. M, Asif A. Shah, Anand Kumar Rai, Rupali Verma, Utpreksh Patbhaje, Jeevesh Kumar and Mayank Shrivastava, “Physical Insights Into the Effect of Substrate on Graphene RF Transistor Performance and Demonstration of Novel Inverted T-Gate Architecture”, in IEEE Journal of the Electron Devices Society, Vol. 13, pp. 930-936, 2025, doi: 10.1109/JEDS.2025.3591152

- Rupali Verma, Utpreksh Patbhaje, & Mayank Shrivastava, “In-plane Field Enabled Dissociation Dynamics of Defect Bound Excitons and Excitonic Oscillator Strength Redistribution in Monolayer WS2”, accepted in ACS Nano

- Utpreksh Patbhaje, Rupali Verma, Jeevesh Kumar, Ansh & Mayank Shrivastava, “Unveiling Inverse Piezoelectricity & Field Induced Nonvolatile Strain in 2D TMDs”, accepted in Nature, npj 2D Materials and Applications, May 2025

- Mohammad Munshi Ateeb, Mehak Mir Ashraf & Mayank Shrivastava, “Enhanced ESD Reliability of AlGaN/GaN MIS-HEMTs using a p-type Oxide Passivation”, IEEE Transactions on Electron Devices, Volume: 72, Issue: xx, xx 2025, DOI: